【核辐射能谱仪/γ射线能谱仪】数字多道脉冲幅度分析器

简介

核辐射测量在核能安全和环境保护等行业中起着重要的作用。其中数字多道脉冲幅度分析器(DMCA)是将核脉冲信号转换为能谱数据的关键设备。本项目旨在设计实现一种基于ZYNQ SoC的便携式数字多道谱仪系统。

简介:核辐射测量在核能安全和环境保护等行业中起着重要的作用。其中数字多道脉冲幅度分析器(DMCA)是将核脉冲信号转换为能谱数据的关键设备。本项目旨在设计实现一种基于ZYNQ SoC的便携式数字多道谱仪系统。开源协议

:CC BY-NC-SA 4.0

(未经作者授权,禁止转载)描述

首先来快速了解一下仪器功能,相比于盖格计数器等计数类仪器,数字多道能够区分核辐射能量,做到核素识别和含量计算!

前排摘要,文章涉及的开发内容:1. 辐射探测基础理论;2. ZYNQ;3. FPGA-Verilog;4. Vitis嵌入式C;5.Qt5 C++上位机; 6. LVGL嵌入式界面;7. MATLAB算法仿真。

如果不想看文章、附件视频3为仪器原理讲解,敬请观看。由于文章涉及理论知识较多,枯燥是难以避免的,请各位见谅。

1. 仪器原理

随着近年来我国经济和社会的高速发展,核辐射测量技术在众多领域中正发挥着关键性作用。如应用于化学、物理及生物学科领域的核分析技术、又如在地球物理勘探中用于研究钻井地质剖面、寻找油气矿藏的核测井技术、以及应用于诸如医疗、环境、原子能、国防等各类领域的辐射探测技术。在这些应用中,核脉冲的幅度是提取分析信息的基础,而多道脉冲幅度分析器(Multi-Channel Analyzer,MCA)在核脉冲的幅度提取与分析中起着十分重要的作用,是辐射测量的关键电子学器件。其原理是将脉冲幅度范围平均分成多个等幅度间隔,这些间隔的数量对应于多道的道数,通过将模拟脉冲信号转化成与其幅度对应的数字量,对落在各个幅度间隔内的脉冲进行分别计数。经过一段时间的累积,就可以得到探测器输出的脉冲幅度的分布曲线,即为能谱曲线。

图1-1 数字多道硬件的基本原理示意

1.1 数字多道整体结构及基本原理

在数字化测量技术出现前,多道脉冲幅度分析器主要由一系列模拟电路组成,经过极零相消、信号放大、滤波成型、基线恢复、堆积判弃、峰值保持等电路后由ADC进行数字化,通过单片机进行幅度谱成形。但由于模拟器件间的差异和易受环境影响的特点,对于高精度高计数率测量已不再适用。随着近年来通用可编程逻辑器件及高速ADC的发展,数字化测量技术已然得到了广泛的应用、数字化多道脉冲幅度分析器也趋于成熟。其主要原理是将探测器前置放大器经过简单的信号调理(极零相消、幅度放大等)后由高速ADC进行数字化采集转而在FPGA等可编程逻辑器件中执行滤波成形、基线恢复、堆积判弃、峰值提取等数字化算法。这些改变为数字化脉冲幅度分析器带来了诸多优点:

- 测量稳定性好,数字算法几乎不受环境因素、时间变化等影响;

- 测量性能优越,极大的减小了电路在处理脉冲时的固有时间。数字算法对核脉冲的处理速度和抗干扰能力都得到了极大提升;

- 体积小巧功耗更低,由于大量模拟器件的削减使得整机功耗明显下降。

数字多道将模拟多道前端大量模拟信号调理电路进行数字化处理,去除了因环境因素和器件差异等引起的谱仪性能变化。数字多道使用高速ADC采样,将经过简单处理的核脉冲信号直接采入FPGA中进行数字化滤波成形,大大简化了电路设计,也提升了谱仪稳定性和性能。

图1-2 数字多道硬件基本逻辑框架

图1-2是数字化多道脉冲幅度分析器的常规组成,主要由探测器、信号调理电路、数字信号处理系统、测量控制系统组成。其各个部分的功能是:

- 信号调理:主要为放大器。由前置放大电路输出的脉冲幅度常在mV量级需要通过主放大器将信号放大至后级电路所需要的范围内。其次还包括极零相消电路,其负责减小脉冲宽度减小堆积;

- 高速ADC:采样核脉冲信号,将信号进行数字化;

- 滤波成形算法:核脉冲信号并不易提取其幅度,通过滤波成形算法将其峰值展宽、补偿弹道亏损的同时也起到低通滤波的作用,常用的滤波成形算法有:梯形成形、高斯成形;

- 基线恢复:通常核脉冲信号是耦合在直流信号之上的,这样提取的幅值是叠加了直流信号量的,通过对脉冲的基线进行提取以恢复脉冲的真实幅值;

- 堆积判弃:在核脉冲信号发生堆积时,其通过滤波成型后的波形将不可使用。通过一定条件的逻辑判断对脉冲是否重叠加以识别,防止错误的幅值信息被采集;

- 峰值提取:提取滤波成形信号的真实幅度信息;

- 能谱成形:真峰的幅值作为道址,对对应道址的数值执行加一的操作;

- 控制端:通常以单片机作为仪器的主控及交互芯片,执行对整个测量任务的控制以及与上位机的交互工作。

通过上述步骤后,形成的能谱存储的便是每个道址在测量期间内积累的幅度值的总计数值,由于核辐射的能量最终是和能谱道址成正比的,那么只需要对仪器进行能量刻度就可以得到道址与能量的关系。

注:上述有许多专有名词,请各位读者不用担心不懂,我也不打算在文字中做解释,因为会严重打断文章的流畅性,读到后续大家会理解它们的。

1.2 NaI(Tl)闪烁体探测器基本原理

γ射线不能被电子学探测器直接探查(非带电辐射),在物质中γ射线会通过:光电效应、康普顿散射及电子对效应与物质相互作用而损失能量(基本原理在视频中有讲解),在探测器内这些损失的能量会转化成电信号从而被探测系统捕捉。当某些物质被激发后原子退激发射出的光子被称之为闪烁,基于这种现象制成的探测器被称之为闪烁体探测器。闪烁体探测器具有探测效率高、衰减时间短、光电截面大等特点,不但可以用于测量核辐射的强弱还可以得到入射射线的能量及其分布情况。

图1-3 闪烁体探测器探头结构示意图

图1-3是闪烁体探头的示意结构,其主要包含以下结构:

- 闪烁体:吸收入射γ射线能量后产生光子;

- 光耦合:减少光子在传递中的反射和损失,使其顺利到达光阴极;

- 光阴极:吸收光子后发射光电子;

- 打拿极:每级打拿极由分压电阻接入高压电源形成高压递增的排列方式,光电子在这些电场中逐渐加速撞击打拿极产生更多电子,逐级倍增;

- 高压分压器:输入高压与地之间串联多级电阻进行分压,电压逐级递减供打拿极使用。

从γ射线进入闪烁体经过上述过程后,会在光电倍增管输出端产生电荷脉冲,为负脉冲,脉冲进入电荷灵敏前置放大器对电荷积分转化为电压脉冲信号后输入后级电路进一步处理。

注:本文研究设计的主要内容为 数字多道脉冲幅度分析器 ,使用的是购买的成品闪烁体探测器(厂商如滨松),其包含闪烁体、光电倍增管、高压电源及前置放大器,故在本文中没有涉及探测器的制作过程!不过在原理图/PCB中,本人设计了正高压+1kV高压电源和电荷灵敏前置放大器,高压经验证可用而前放未经验证。在这里放出光电倍增管分压电阻网络的两种常用设计方案(配合正负高压电源使用),如图:

1.3 能谱数据的定性分析和基本处理方法

为了各位能够快速了解本文设计的仪器的作用,这里首先放出测量结果作为展示,如图1-4:

图1-4 Co-60&Cs-137混合放射源测量结果(500s)

上图是本文设计的上位机软件,在后文会做介绍。可以看大测量的能谱中有几个明显的峰值,从左至右第一个小尖尖是Ba-137(Cs-137的衰变子体)的特征X射线,能量32keV、很宽的那个是康普顿坪和反散射峰、第三最高峰为Cs-137的全能峰,能量662keV、第四第五为Co-60的两个全能峰,能量1173&1332keV。

那么,大家可以知道,辐射能谱相比于盖格计数器、个人剂量率仪,能够非常精确的分辨放射性核素的能量和种类。在前文我们提到道址与射线能量是成正比的,那么根据上图已知能量核素测量后,我们能够找到峰值道址与能量的对应关系,这样进行线性拟合(能量刻度)就可以得到每个道址对应的能量,那么在测量位置环境的时候就可以根据能量进行核素识别了!

当然,本仪器不只是有这样定性分析的能力,根据峰值的左右边界确定核素的计数可以进行定量含量分析!(这就需要更具体的算法支持了,后文将提到)

- 能量刻度(找出道址与能量的线性关系系数)

- 谱光滑(平滑谱线);

- 寻峰(找出谱图中的峰值及其左右边界)

- 核素识别(根据数据库给出能谱中探寻到的核素种类)

- 峰面积计算(计算能谱峰的净峰面积)

- 含量计算(根据净峰面积、测量时间、探测效率等因素计算核素含量)

上述几个步骤是通常的能谱数据处理流程,前四点都是定性分析,由于工程量巨大,本文上位机软件只做到了寻峰步骤,核素识别需人工识别。后续定量分析都需要手动计算了。

图1-5 环境本底辐射测量结果(1800s)

上图1-5是环境本底的测量结果(非常标准的环境本底能谱),在1800s的测量中可以发现在447~511道之间有峰的存在,该峰是1.46MeV天然K-40的贡献(就是香蕉里那个K-40)。其次在大于511道之后放大还可以看到天然放射性系列:铀钍系的贡献(那就很小了)。

以上我相信大家对该仪器的原理、应用及结果都有了初步的了解,那么接下来就开始进入仪器设计部分了。

2. 系统方案与硬件电路设计原理

2.1 系统设计方案

图2-1 数字多道系统设计整体逻辑框架

本文数字多道系统基于Xilinx ZYNQ SoC异构芯片进行设计,该芯片在传统FPGA架构的基础上搭载双核ARM-Cortex A9处理器,为高速数据采集任务提供优秀的性能支持。系统整体架构如图2-1所示,探头部分集成高压电源与电荷灵敏前置放大器;信号调理部分首先通过极零相消电路将核脉冲宽度减小、经过主放大器进行幅度放大、后通过ADC差分驱动将单端信号转换为差分信号最终输入ADC进行数字化采集;采集的信号在ZYNQ FPGA中进行数字化处理并形成能谱数据;通过ZYNQ芯片内部高速总线将能谱传输至ZYNQ ARM端进行上下位机数据传输和整机控制。

进一步细化硬件部分:

图3-2 数字多道硬件设计逻辑框架

本文设计硬件可以大致分为三个部分:测量采集、控制传输、电源管理。测量采集包括探头、高压及前置放大器。这些部件通过屏蔽电缆连接至主机的信号调理输入端,并经过极零相消、主放大器放大、电压转换、单端转差分后进入ADC进行实时采样转换。控制传输部分主要包括ZYNQ核心板,用于ADC采样控制与脉冲数字成型、整机控制、上下位机数据传输等工作,通过控制串口、以太网口、LCD触摸等外设实现。电源管理包括4.2V锂离子电池充放电管理、数字电源5V转3.3V及1.8V,以及模拟电源5V转+9V及-9V DCDC。模拟电路后级使用LDO,设计输出+5V、-5V、3.3V、1.0V供信号调理及ADC芯片使用。

2.2 信号调理电路原理及设计

由于涉及到一些专业知识,所以在此对信号调理电路进行着重说明,而数字电路设计参考正点原子ZYNQ领航者开发板设计,在此不做重点讨论。

2.2.1 极零相消电路(PZC)

对于电荷灵敏前置放大器(Charge Sensitive Amplifier,CSA)输出的脉冲信号的后沿下降较慢,在高计数率下信号在尾部会出现脉冲堆积,引起基线漂移,脉冲叠加后会导致后级放大器无法正常工作,故通常使用极零相消电路(Pole-Zero Cancellation,PZC)减小脉冲宽度,使探测系统在高计数率下仍能保持正常工作。

图3-3 极零相消电路示意图

图3-3是PZC电路的示意图,在使信号快速下降的同时解决了CR微分电路造成的信号下冲现象。

根据基尔霍夫电流定律与s域变换公式易知:

(其时间常数是必然减小的,仪器设计电路与图3-3一致,不做过多展示)

2.2.2 主放大器

本文选择了ADI公司的LTC6228运放芯片。LTC6228是单通道高速低噪声的轨对轨输出、单位增益稳定的运算放大器。

图3-4 主放大器电路原理图

图3-4是本文采用的主放电路原理图,为了适应更多前放的输出模式,在本文中所设计的主放同时兼容了负脉冲和正脉冲的输入,故采用了两级反相运放电路,第一级为主放大器负责将输入信号放大指定倍数,而第二级运放设置为单位增益负责信号的反相处理。后续使用模拟开关选择运放输出。

为了满足多路复用的要求,本文选择了ADI公司的模拟开关芯片AGM1419实现信号选通功能,图中标签“MUX0_A0”是输入数字信号用于选择通道,连接至ZYNQ核心板进行控制。

2.2.3 电压变换电路

为了配合后级ADC采样电路,直接输入0V~+5V范围的脉冲信号是不可行的,因为本文所采用ADC差分输入范围在2Vpp,故需要使用运放电路将脉冲幅值变换到-1V~+1V范围内!分析后可以得到二者的关系服从:

那么对于幅值变换部分可以使用分压电阻与运放设计实现,而涉及加减运算可使用加法器实现。将两者结合即可得到电路如图3-5所示:

图3-5 运放电压变换电路

电路中+1V参考电压由前文所述LT3045 LDO电路产生。

2.2.4 ADC差分驱动及采样电路

本文选择了ADI公司的AD4945-1差分运放芯片。ADA4945-1是一款低噪声、低失真、全差分放大器。

图3-6 AD4945-1单端转差分电路原理图

由于AD9245要求输入共模电压为1.65V,那么可以简单的对3.3V分压获得,如图3-6中电阻R82与R88。其次,由于电源电压难免会出现偏差且模拟器件的差异可能会出现输出差分信号差值超出ADC要求范围的情况,为了保证差分输出信号的差值始终保持在ADC要求范围内(AD9245为2Vpp),差分运放负输入端不再接地(接地则连接电阻R85,建议直接接地!)而接入可调电阻提供一个在-5V~+5V范围内供手动调整脉冲基线电压。

对于ADC,本文选用的ADC为ADI公司的AD9245 14Bit@80MSPS逐次逼近型转换芯片。

图3-7 AD9245电路原理图

图3-7是AD9245的电路原理图,芯片采用CMOS输出,对其数字信号引脚进行阻抗匹配采用电阻,在后期PCB设计中需重新计算布线阻抗信息。“Mode”引脚是芯片的模式选择引脚,可以配置输出数字信号的格式、以及进行外部时钟稳定,根据数据手册将引脚设置为2/3Vcc时输出数据格式为二进制补码、输入时钟稳定。“SENSE”引脚可设置差分输出范围及参考电压值,本文接地即设置为2Vpp范围、输出参考电压1V。“REFT、REFB”为内部参考电压去耦管脚,外接去耦电容。

另外,为了保证芯片的性能,输入ADC的差分信号经过了抗混叠滤波器,这里电阻电容提供了一个低通滤波器及为ADC内部的采样保持放大器提供充电保持。其带宽计算公式:

那么取 时,计算得该滤波器带宽为40.19MHz。

时,计算得该滤波器带宽为40.19MHz。

2.3 数字电路设计

本文选择了正点原子的ZYNQ7020核心板。其次LCD采用了正点原子4.3英寸RGB888协议LCD显示器,数字部分包括TF卡、以太网、USB2.0参考正点原子开发板设计。(由于没有使用USB2.0功能,该部分可以不用焊接)

其次,PCB串口使用了TypeC和TypeB双接口的设计,仅仅是简单的并联关系,实际使用可仅焊接TypeC即可。该接口负责串口通讯和充电。

2.4 PCB整体布局

本文所设计多道脉冲幅度分析器PCB主板经过修改验证最终版本如图3-8所示。PCB尺寸140x90mm,布局较为紧凑性能良好。

图3-8 PCB电路整体布局

3. 数字成形算法——梯形成形的研究

首先解答最重要的问题,为什么必须使用数字成形算法?其一,为了缓解弹道亏损效应的影响:由于分布电容及电阻的影响导致理想核脉冲(单指数衰减信号)的上升沿不再理想,而具有了一定的宽度,最终变为双指数衰减信号,这导致了脉冲幅度的衰减,称之为弹道亏损(导致能谱整体往低能区飘移);其二,数字滤波成形算法作为数字滤波器的一种,具有一定的滤波作用。

现如今已经发展出了较多的数字成形算法,其中梯形(三角)成型由于其算法简单实时快速利于高通过率脉冲、能够减小电子学噪声和弹道亏损、提高能量分辨率、降低对ADC微分非线性的要求等优点被广泛的应用于数字多道中。

3.1 梯形成形算法的数学描述

在理想情况下,核脉冲信号的数学表达式为:

其中A是脉冲的幅度、τ是信号衰减时间常数、u(t)是阶跃函数。

所谓梯形成型就是将核脉冲信号成形为等腰梯形信号,其中三角信号为梯形平顶宽度取为零时的特殊情况,如图3-1所示:

图3-1 梯形成形信号

将图3-1转换为函数式表达:

上式中ta表示梯形达到平顶前的上升时间宽度、tb为平顶结束时刻的时间、tc为整个梯形的时间宽度。

在实际应用中,实现梯形(三角)成形的方式通常有两类:Z变换法和卷积变换法。由于Z变换法推导的算法在FPGA中易于实现,故本文选择了使用Z变换法推导的梯形成形算法。对上两式离散化处理后进行Z变换,得到系统的响应函数:

假设系统的采样周期为,则式中 。

。

可以观察到式上中存在反馈单元,其属于IIR滤波器。为了减小FPGA成形算法的实现难度,将多阶滤波器拆分以级联的方式实现,本文将响应函数拆分为四个子系统级联:

将上式进行逆Z变换,得到:

上式中,易知子系统H1(z)&H4(z)为微分运算,而H2(z)&H3(z)为积分运算,将H1(z)置于第一级可以避免积分过程的数据溢出,而H4(z)置于最后可减小积分中累计的误差,但会使用更多的FPGA资源(7020资源足够,不担心)。

3.2 梯形成形算法的仿真研究

3.2.1 成形参数对堆积脉冲分离的影响

在自然界中放射性衰变具有随机性,会出现短时间内发生多次衰变的可能。在这种情况下前一个核脉冲还没有完全恢复到基线时第二个脉冲就到来了,这样第二个信号就叠加到了上一个信号的尾部,我们称之为脉冲堆积。脉冲堆积会造成脉冲的幅值变化从而提取到错误的信息,而数字成型算法有一定的堆积分离能力,其与具体的成形参数有关,所以研究不同的成形参数对堆积脉冲的分离能力是必要的,也可为后文的堆积判弃模块提供理论参考。

本文使用理想核脉冲进行研究,如图3-3两脉冲间隔100个时钟周期。首先固定梯形上升沿宽度na=20,仅改变平顶宽度研究其对堆积脉冲成形的影响,结果如图3-3:

图3-3 仅改变nb值对堆积脉冲梯形成形的结果

可以发现随着平顶宽度的减小,成形脉冲的堆积情况也得到缓解。在图3-3中当nb=100时可以发现此时前一信号的成形脉冲下降沿消失而后一信号的成形脉冲上升沿消失,两平顶正好连接到一起,此时是能够分离堆积脉冲的极限情况!进一步分析,这里nb=100是梯形成形信号的上升沿和平顶的宽度之和与前文提到的两堆积核脉冲的间隔宽度是相等的,那么当继续减小时两梯形信号间隔越来越大而当nb大于这个临界值时梯形脉冲的平顶开始堆积,此时无法再继续提取脉冲峰值,堆积峰被丢弃,反之不然。故在梯形成形上升沿宽度固定时其平顶越窄,分离堆积脉冲的能力越强。

图3-4 仅改变na对堆积脉冲梯形成形的结果

图3-4是在固定梯形成形平顶宽度一定时(nb-na=60)改变其上升沿宽度来研究其对堆积分离的影响。很明显我们可以发现梯形脉冲的堆积情况随着na的减小而减小,同样的当nb=100时可以发现两脉冲平顶刚好平齐。故结合前文结果,可以得出梯形成形对堆积核脉冲的分离能力受到成形宽度的影响,当成形参数nb值小于等于两核脉冲间隔时堆积脉冲的峰值可以被完整提取,当na+nb小于等于两核脉冲间隔时梯形成形脉冲可以完整的将堆积分离。

3.2.2 成形参数对噪声抑制的影响

实际测量电路中的电子学噪声是不可避免的,为了保证高频噪声不至于干扰幅值提取的过程,Z变换推到的梯形成形算法作为IIR低通滤波器对高频噪声有一定抑制效果。该低通滤波系统的截止频率与梯形成形的参数密切相关。

图3-5 仅改变na值梯形成形对噪声滤除的效果

为了研究成形参数对梯形成形滤波效果的影响,这里使用叠加高斯噪声的理想负指数衰减信号进行试验。图3-5是在固定梯形脉冲平顶宽度(nb-na=50)对比不同上升沿宽度条件对滤波效果的影响,可以明显看出随着上升沿宽度的增大输出梯形脉冲的高频成分越来越少。故梯形上升时间越长滤波效果越好,其截止频率越低。

图3-6 仅改变nb值梯形成形对噪声滤除的效果

图3-6是固定梯形上升沿宽度对比不同平顶宽度条件下对滤波效果的影响,显然随着平顶宽度的变化梯形脉冲的滤波效果没有出现明显的改善,故结合前文可以断定滤波效果仅与梯形成形的上升时间相关,且越长越好。

综上,结合滤波效果和去堆积效果可以发现其取值对结果的影响恰好是相反的,那么我们在FPGA上实现算法时就需要综合考虑噪声水平和测量的核脉冲堆积的严重程度来综合选择一个恰当的成形参数。

本章的研究内容主要是用来指导后续成形参数设置和FPGA逻辑设计的。非常重要!

4. 梯形成形的FPGA实现

4.1 算法整体框架

图4-1 FPGA算法逻辑框架

FPGA算法部分基于Z变换法推导的梯形成形实现。首先ADC采入数据进入FIFO缓冲后经过FIR低通滤波器输出降噪后的核脉冲信号,对脉冲进行梯形及三角混合成形,利用三角成型便于寻找峰顶的特性可以更准确的确认核脉冲到达、梯形成形用于提取脉冲的幅值。后根据脉冲起始信号将梯形脉冲用于提取基线和幅值,之后根据堆积判弃的结果确认当前计算的幅值是否可用于最终的能谱成形,并将谱数据通过DMA搬运到PS端DDR3存储器中。

在FPGA中为了小数方便运算,通常以定点小数形式存放,混合成形算法中存在大量的小数和有符号数的运算,在后文代码编写中统一采用固定小数位为30Bit的方式来截断表示。

4.2 梯形三角混合成型

梯形三角混合成形均采用Z变换法推导的梯形成形算法实现。根据第四章推导递推式将整个成形过程分为四个模块进行:模块1实现输入信号延时、模块2、3实现积分求和、模块4实现信延时。

模块1将输入的原始脉冲信号进行延时时钟周期的操作,在FPGA中延时可以使用一定存储深度的寄存器进行移位操作实现。

- always@(posedge sys_clk)

- begin

- if(!sys_rstn) begin

- for (i=0; i

- delay_temp[i] <= 15'd0;

- end

- end

- else begin

- delay_temp[0] <= {1'd0,adc_fifo_datain};

- for (i=0; i

- delay_temp[i+1] <= delay_temp[i];

- end

- end

- end

上述代码使用了一个存储深度为“REG_GLOBAL_LIMIT”(定义参数,本文取400)的15Bit有符号寄存器“delay_temp”进行移位操作。在全局复位时将寄存器进行清零,其中的for循环是固定次数的,可综合实现。在电路正常工作时,首先将输入信号存入第一个寄存器然后每个时钟周期对整个寄存器进行移位操作,最终我们只需要在另一个always语句块中取出对应的第个数据就实现了延时操作。

但需要注意的是用户实时给定的成形参数和均不能超过寄存器的存储深度(不大于“REG_GLOBAL_LIMIT”)。

模块2求解的积分包含了乘除法运算,为了加快计算速度,这里将式(4-5)中的除法运算在PS端使用FPU(Floating Point Unit,浮点处理单元)进行处理,对小数扩大倍后传入FPGA中进行乘法运算,由于ZYNQ PL端资源包含较多DSP可以轻松的应对乘法运算。

- assign multiple_temp1 = trapezd_alg_m1_datain * na_1;

- assign multiple_temp2 = vi_delay1 * d_na;

- always@(posedge sys_clk)

- begin

- if(!sys_rstn) begin

- trapezd_alg_m2_dataout <= 52'd0;

- vi_delay1 <= 16'd0;

- end

- else begin

- vi_delay1 <= trapezd_alg_m1_datain;

- trapezd_alg_m2_dataout <= trapezd_alg_m2_dataout + multiple_temp1 - multiple_temp2;

- end

- end

将上一模块的结果作为输入接入该模块,其中,均由PS端计算后传入。上述代码求和过程看似没有对信号进行延时,但右侧取值实际是上一时钟周期内“trapezd_alg_m2_dataout”的值,符合时序。注意由于此模块引入了定点小数运算,故寄存器扩大至52Bit,其中后30 Bit为小数位。

模块3主要实现了简单求和,只需要注意下时序即可。

- always@(posedge sys_clk)

- begin

- if(!sys_rstn) begin

- trapezd_alg_m3_dataout <= 52'd0;

- vi_delay1 <= 52'd0;

- end

- else begin

- vi_delay1 <= trapezd_alg_m2_datain;

- trapezd_alg_m3_dataout <= trapezd_alg_m3_dataout + vi_delay1;

- end

- end

模块4实现了差分与延时,延时原理与模块1一致。

- assigntrapezd_alg_m4_dataout = trapezd_alg[29] ? (trapezd_alg[47:30] + 1'b1) : trapezd_alg[47:30];

为了将最终结果截断为整数,上述代码实现了四舍五入的判定。计算可知十进制0.5(D)的二进制表示为0.1(B),那么对小数部分最高位进行判断如果为1(B)则整数部分加一进位,不是则直接截去小数部分。

图4-2 梯形三角混合成形算法仿真

将上述模块在顶层中进行例化,后使用Vivado提供的仿真工具编写Testbench文件对算法进行仿真测试。将MATLAB生成的带噪声的负指数脉冲信号作为输入,计算好合适的成形参数后可以发现算法成功的将其成形为了梯形信号和三角信号,如图4-2所示。

4.3 脉冲起始检测

由于三角成形的特性,只需要找到其峰顶便可以判断核脉冲的到来,为后续判断逻辑提供精确的触发。(为了减少篇幅,后续Verilog代码请自行参考文件)代码中将输入的三角成形值中前后三点进行比较从而判断是否为峰值,其次为了防止噪声干扰,还需要满足阈值“peak_threshold”条件,该值由用户确定。为了进一步避免噪声干扰将记录满足峰值条件前超过阈值的数目“threshold_count”,需要其大于用户设定的数目,这是为了避免大幅度噪声干扰引起的误判。最后使用“interval_count”来规定两个脉冲来临的最小间隔,若系统判定两个脉冲间隔太小则认为第二个为假脉冲,这是为了避免噪声叠加在满足阈值条件的三角成形脉冲上导致的误判。

4.4 脉冲堆积判弃

第四章对堆积脉冲分离的理论情况进行了详尽的研究,得出了结论:当脉冲间隔大于等于梯形成形的上升时间与平顶时间之和时可以被分离,也就是当间脉冲隔时间不小于时可被分离。代码中“min_interval”代表最小间隔值(赋值为),always模块中使用脉冲起始信号作为触发进行计时,且计时到达“min_interval”时将保持不变。在另外的always模块中判断两相邻脉冲间隔是否小于可分离的最小间隔,如果是则输出堆积脉冲标志“stacking_flag”。

4.5 脉冲基线提取

本模块依然需要根据脉冲起始信号进行逻辑判断,但是当脉冲起始信号触发后梯形成形已经到达峰值位置了,如果以该点作为基准往前求几个点的均值作为基线数据显然是错误的,所以需要对梯形成形信号进行延时,延时时间为个时钟周期(AVR在此处代表均值点数目,本文取8点),那么此时脉冲起始信号触发后对延时数据进行均值计算便为正确的基线数据。

数据延时原理与前文一致,但还需要注意的是当堆积发生时梯形成形可能出现重叠的情况,此时脉冲可被分离但求解后一信号的基线显然是不合适的,需要使用算法逻辑避开此类情况并使用前一信号的基线作为当前值。由前文对堆积情况的理论研究可知,只要需要两脉冲间隔大于时才可提取后一信号的基线,该判定也通过计数器实现。

4.6 脉冲峰值提取

有效峰值的计算需要根据前文堆积判弃的结果进行判断才能做出进一步的动作。由于判定堆积需要联系前后两个脉冲的关系,故在脉冲起始信号发出后需要对当前峰是否发生堆积以及前一脉冲是否发生堆积进行判定,再对梯形成形进行峰值提取。判断逻辑较为复杂,本文使用有限状态机实现。

图4-3 峰值提取逻辑状态转换图

图4-3是状态机的状态转移图,首先在没有脉冲起始信号到来时状态机在“WAIT”状态等待。

- 情形1:当脉冲起始信号到来、当前脉冲未发生堆积且前一脉冲也未发生堆积则立刻输出前一脉冲的峰值信息供能谱成形模块使用。然后开始计算当前脉冲的幅值,首先转移到“DELAY”状态进行用户指定的延时(用户可以指定在梯形平顶处延时多长时间后才开始求取平均以便得到更准确的幅值),延时结束转移到“ACC”状态求32点的均值,最后转移到“BASELINE”状态减去基线求解真幅值,至此当前脉冲幅值计算结束并返回“WAIT”状态等待。其次,在计算过程中不管任何状态只要发出堆积信号则立刻跳转至“PILE_UP”状态复位寄存器并回到“WAIT”状态等待,即抛弃当前峰值和刚到来的堆积峰;

- 情形2:当脉冲起始信号到来、当前脉冲未发生堆积但前一脉冲发生堆积,相比于情形1差异就是不输出前一脉冲的峰值信息,后续流程一致;

- 情形3:当前脉冲发生堆积,抛弃且继续在“WAIT”状态等待。

对上述算法逻辑进行仿真,结果如图4-4:

图4-4 成形及判断算法逻辑仿真结果

可以看到在第一个红框内,脉冲到来时“peak_start_flag”触发。此时输出计算好的基线值“trapezd_baseline”,其次由于该信号是第一个输入脉冲,故此时既无堆积也无上一脉冲幅值信息的输出。在第二个红框处脉冲再次到来可以看到此时输出了前一脉冲幅值和“peak_value_ok”信号用于触发能谱成形模块。堆积脉冲到来时,第三个红框可见堆积信号“stacking_flag”触发,此时并未输出前一脉冲的幅值且基线值也保留了前一峰的计算结果(间隔不足以计算基线)。第四个红框可见当后续脉冲到来时也没有输出前一堆积脉冲的幅值,可见两堆积脉冲被成功丢弃。多个峰堆积以此类推。

4.7 其他

我认为其他部分不必再叙述了。其中FIR为MATLAB联合IP核设计的、DMA使用AXI IP核。由于FPGA工程较大、逻辑比较复杂,可能很难看懂,也请见谅。如果需要修改为自己的硬件连接,请修改引脚约束后再重新综合实现。

Vivado与Vitis开发环境的搭建请自行参考Xilinx教程文档。

5. 嵌入式软件设计

5.1 整体框架

图5-1 ZYNQ SoC PS端应用程序逻辑框架图

本文PS端程序主要由两大部分组成,分别运行在两颗CPU核心上。双核心工作在AMP(Asymmetric Multi-Processing,非对称多处理)模式下。AMP模式指每个内核运行自己的OS或不同独立实例。在运行裸机时,每个内核有自己独立的内存空间,也可以和其它内核共享部分内存空间,每个核心相对独立地运行不同的任务,但其中一个核心为主核心,负责控制其它核心以及整个系统的运行,而其它核心负责配合主核心来完成特定的任务(Xilinx,2014)。在本文的应用中,双核CPU各自占用DDR3内存的一半作为独立访问的缓存区域,而双核的数据交互通过片内OCM缓存配合软件中断进行交互。CPU0作为主核心用于系统初始化、CPU1的启动、上下位机传输、外设控制及测量控制,而协处理核心CPU1只负责处理图形化用户界面、触摸等输入操作。图5-1是整体的裸机软件逻辑框架。

以下关于嵌入式和上位机软件具体代码就不多讲解了,参考文件。

5.2 串口与以太网通讯

ZYNQ SoC PS端自带UART外设,设定波特率为921600Bps后便可以正常收发数据。需要注意的是在ZYNQ中整个SoC的中断均由GIC(General Interrupt Controller,通用中断控制器)管控,故在初始化后必须初始化GIC才能保证整个中断系统的正常运作。

千兆以太网协议层的实现使用了LwIP(Lightweight IP)开源协议栈。LwIP是一个开源TCP/IP(Transmission Control Protocol/Internet Protocol,传输控制协议/因特网互联协议)协议栈,其具有轻量级、可裁剪性、高性能、可移植性等特性。由于其占用内存较小、整体代码量较小使其适合于嵌入式系统中的使用。本文中将协议设置为静态IP分配,固定默认IP地址为:192.168.1.10,默认端口为:7。(具体配置参考网络)

5.3 TF卡数据存储

为了方便管理TF卡文件,本文引入了开源FatFS文件系统作为谱文件存储的方式。FatFS开源嵌入式文件系统提供了统一的API接口函数用于读取,写入文件、格式化、创建分区或磁盘等等。且Xilinx官方已经为ZYNQ移植FatFS文件系统,在Vitis中可以方便的配置和使用。

5.4 嵌入式LVGL图形化交互界面设计

LVGL(Light and Versatile Graphics Library,轻便通用图形库)是一个开源的图形用户界面库,旨在为嵌入式系统提供轻量级、可移植、灵活和易于使用的图形用户界面解决方案。LVGL的核心代码使用C/C++语言编写,可以在不同的操作系统、微控制器和图形加速器上运行,其轻量级、多功能、灵活、可移植、易用性等诸多特性使其非常适用于嵌入式系统。使用LVGL比较困难的步骤在于移植,需要针对特定芯片和外设进行定制化操作,主要在于输入输出硬件的驱动连接。为了方便移植,LVGL在顶层给出了各类不同输入设备的接口,如按键、触摸、摇杆等,本文使用到的是电容式触摸LCD显示器,只需要将触摸屏驱动完成将获取到的坐标信息传输给LVGL即可。对于屏幕显示信息LVGL提供的方案是使用“显存”,即在ZYNQ DDR内存中开辟专用空间进行图形渲染,然后用户将图像信息及时搬运到屏幕上,本文使用了PL端DMA进行图像帧数据的搬运。

6. PC上位机软件设计

6.1 整体框架

图6-1 Qt上位机程序逻辑组成框架图

图6-1是整个上位机的程序逻辑框图,主要可以分为下位机交互、文件管理、用户控制、谱数据处理和图表绘制部分。软件的整体逻辑为:当用户在上位机软件上启动测量时,上位机通过串口或以太网下发成形参数和启动测量命令,此时上位机开始定时。每间隔特定时间上位机通知下位机上传能谱数据,这样上位机图表就能及时更新显示数据。当上位机定时到达时下发停止测量命令终止整个测量并将最终谱图更新到上位机中。

6.2 谱光滑算法

程序集成了算术滑动平均法,其通用公式可以表示为:

依照基本算法,本文上位机实现了用户自定义滑动点数,用户可以输入1~255之间的所有奇数值用于滑动滤波,基本原理就是多点求平均。但是该方法不推荐使用,光滑后会引起谱峰展宽导致能量分辨率变差!

其次软件也集成了常用的3点、5点、7点重心法用于谱光滑,根据推导公式:

推荐使用,具体操作界面如图6-2:

图6-2 上位机光滑算法界面

在打开谱图文件后,一般请将道址数量从16384缩小至1024或2048道!选择光滑后,主界面出现的红色谱线就是光滑后的谱线,点击右下角按钮“光滑谱线”可打开/关闭原始谱线的显示。

6.3 对称零面积寻峰算法

为了提高对弱峰的寻峰能力,本文选择对称零面积算法并使用零面积高斯函数作为变换函数。该算法的基本思想为:面积为零的窗函数与谱数据进行卷积变换,其对线性基底的卷积变换将为零,只有存在峰的地方不为零。因此对谱数据的对称零面积变换谱将反映峰形的变化。卷积的数学表达为:

其中Cj是变换函数、datai是原始谱、yi是卷积变换谱、窗口宽度W=2m+1。本文中高斯变换函数的数学表达为:

该算法一般使用变换谱的标准偏差为单位找峰,当该值超过某整数f时认为该道址为峰位,其数学表达为:

具体操作界面如下图6-3所示:

图6-3 对称零面积寻峰操作界面

在打开谱图文件后,一般请将道址数量从16384缩小至1024或2048道!首先在弹出的对话框中输入高斯函数宽度和窗宽(没有特定值要求),点击开始卷积可以得到右侧转换后的谱图,一般对于有峰的位置都会有比较明显的突起。之后根据卷积结果选择合适的寻峰范围和阈值f。就可以寻出想要的峰位和峰边界。

6.3 SNIP本底扣除算法

在能谱测量中由康普顿效应、γ射线在探测器内小角度散射和天然本底会引起能谱本底计数增加从而埋没部分峰值。为了更准确的计算峰的净计数,必须先扣除谱线中的本底计数。本文选择了最常用的SNIP算法。

算法首先对计数进行对数变换以提高对弱峰的识别能力:

式中x(i)为原始第i道对应计数,y(i)为变换后对应的计数。

算法的滤波窗口宽度为W=2m+1,根据算法需要对变换后的谱线数据进行迭代。在第m次迭代中需要使用上一次迭代m-1中的值: ,取其最小值赋与ym(i)。其数学原理如下:

,取其最小值赋与ym(i)。其数学原理如下:

迭代完成后可获得谱线的本底的对数谱,根据式进行反变换即可得到本底谱,使用原始谱减去本底谱即完成本底扣除。

具体操作界面如下图6-4所示:

图6-4 SNIP本底扣除操作界面

图6-4是对137Cs原始谱去除本底的操作结果。可以看到在计算界面用户可自行输入窗宽大小,参考右侧图表调整窗宽使红色曲线(本底对数谱线)最佳。在主界面中蓝色曲线为扣除本底后的能谱,黑色为原始谱,对比两谱线137Cs峰发现本底得到有效扣除。

7. 整机测试与评价

7.1 ADC采样噪声评价

将数字多道的输入悬空,接入JTAG下载器,启动能谱采样后使用Vivado软件导出ADC实时采样数据。表7-1中,类型1为输入悬空的结果。采样三组数据,每组16384个点,分别求解每组中波动范围后取三组平均得到ADC采样的自身波动。类型2在PCB上断开ADC差分驱动输入端信号使之悬空重复上述操作,得到如表7-1所示结果:

表7-1 ADC采样噪声波动范围

|

类型 |

波动范围(道址) |

|

1 |

50 |

|

2 |

10 |

前文提及ADC输入电压范围为2Vpp,对于14Bit的ADC,对比类型1与2的结果可知,采样噪声主要来自运放电路。ADC自身采样的波动约1mV,而类型1的波动在6mV左右,这意味着PCB设计仍有优化空间。

7.2 仪器线性度与通过率测试

将主放增益降低,使用负指数脉冲发生器产生不同幅度的脉冲信号,输入数字多道中进行测量,并找出峰值对应的道址,输入5mV、50mV、100mV、300mV、500mV、800mV、1000mV的信号序列,测量得到如图7-1所示的电压-道址关系拟合曲线:

图7-1 输入脉冲电压与道址拟合曲线

如图7-1,根据拟合结果可知仪器的道址与能量之间具有良好的线性关系,为0.9999。

使用60Co、137Cs混合放射源进行测量,后使用本文设计上位机软件寻峰后拟合能量与道址,结果如图7-2所示:

图7-2 NaI(Tl)探测器测量混合源原始谱图及拟合曲线

可以看到图7-2中,从左至右分别是137Ba 32.0keV特征X射线峰、137Cs 662.0keV全能峰、60Co的1173.2keV及1332.5keV全能峰,使用四个峰位道址与能量进行拟合,可以看到道址与能量之间具有良好的线性关系,为1.0000。

图7-3 固定幅度核脉冲发生器

为了测试仪器的脉冲通过率情况,使用负指数信号发生器产生固定幅值、频率不同的核脉冲用于测试,信号发生器如图7-3所示。设置不同的脉冲频率,每组测量120s,每种频率通过率取三组平均,结果如图7-4所示:

图7-4 不同频率的脉冲通过率曲线

由于没有对活时间进行矫正,所以通过率并未达到100%。通过图7-4中结果可以发现在没有堆积、固定幅值的核脉冲条件下仪器几乎没有抛弃任何输入脉冲。

7.3 仪器能量分辨率测试

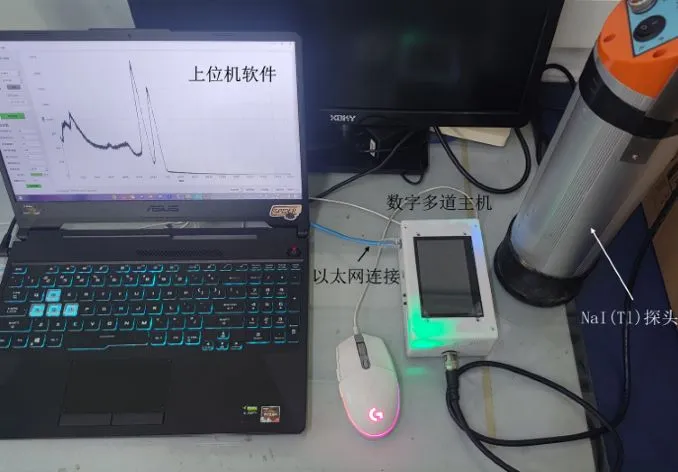

能量分辨率表征了仪器对不同能量射线的分辨能力,是能谱仪器的重要指标参数,使用峰半高宽与峰位道址的比值表示。为了测量仪器的能量分辨率情况,组建了如图7-5的测试环境。

图7-5 数字多道测量评价环境

本文使用不同的探测器对放射源进行测量评价,分别使用NaI(Tl)探测器(如图7-5)与CeBr3探测器对137Cs源进行360s测量,原始能谱图如下:

图7-6 NaI(Tl)探测器测量137Cs原始能谱图

使用Na(Tl)探测器测量结果如图7-6所示,其分辨率为7.30%@662keV,符合NaI(Tl)探测器的能量分辨率特征。而使用相同探头的IED-3000B型探测器分辨率为7.69%@662keV,仪器性能优于IED-3000B型探测器。

图7-7 CeBr3探测器测量137Cs原始能谱图

使用CeBr3探测器测量结果如图7-7所示,该探测器标称分辨率为4.2%@662keV,测量结果劣于标称值,可知这部分分辨率损失主要由PCB噪声干扰引起。

7.4 仪器稳定性测试

为了验证仪器的稳定性情况,本文在实验室内将数字多道连接探头后对环境本底进行连续测量,每次测量1小时,共测量八次,不间断测量。最终以K-40峰位道址作为评价条件,得到表7-2所示结果:

表7-2 稳定性测量K-40道址结果

|

测量序号 |

道址 |

|

1 |

476 |

|

2 3 4 5 6 7 8 |

476 476 476 476 476 475 476 |

表7-2是将16384道数据合并至1024道后光滑寻峰得到的结果,可以看到K-40的峰位道址在八小时连续测量中仅变化1道,系统长期稳定性良好。

其次使用低活度137Cs源进行八小时稳定性测量,每组600s,每一小时测量一次共八次。以验证在一天的间断测量过程中仪器的稳定性。

表7-3 稳定性测量137Cs道址结果

|

测量序号 |

道址 |

|

1 |

216 |

|

2 3 4 5 6 7 8 |

216 216 216 216 216 216 216 |

表7-3是最终测试的道址数据,在8小时的间断测量中137Cs全能峰对应的道址未发生变化,仪器的稳定性良好。

8. 其他

8.1 仪器的参数设定讲解

上位机与LCD上参数设置一致,如下:

- 测量时间S:测量时间,单位:秒(sec);

- 上升时间Na:梯形/三角成形的上升时间;(建议小于200);

- 平顶时间Nb:梯形成形的平顶+上升沿时间!(不大于400);

- 成形参数d:核脉冲的衰减时间常数,可以使用MATLAB拟合计算;

- 峰判定阈值:三角成形中大于该值才判断为真脉冲,根据基线做调整;

- 峰均值延迟:在梯形成形峰顶延迟多少个时钟后再开始提取平顶均值(FPGA“中固定采集32点求平均,故该值+32不能大于平顶时间!)

- 峰判定延迟:在三角成形中不仅需要大于5)中的阈值,还需要满足连续多个点均大于阈值,否则可能将噪声尖峰脉冲错判。(根据噪声水平设置)

具体的成形参数设定可根据实际情况和第3章分析协调。

8.2 3D外壳及组装

除了最主要的PCB设计外,本文还设计了3D外壳和电池组,电池组PCB见下文,为了白嫖免费打印次数,6组并联电池由3组的PCB两块焊接而成!!如下图:

外壳的话直接打印即可(LCD的4个螺柱设计尺寸有误还未更改,我直接用热熔胶粘上的!),没有过多的安装要求,全部使用M3的螺柱螺丝螺母。注意,电池与主PCB间螺柱建议使用5mm塑料柱子,其次不用18650也行,可以去淘宝买10000mAh的那种刀片的充电宝的电池,贴背面就是了。甚至不用电池也可以,直接插充电器就行了。

8.3 总结与寄语

本项目为本人本科毕业设计课题,这里专门摘出大家能够实现的部分用于核辐射能谱采集的数字化多道脉冲幅度分析器,设计实现了其完整的功能。

其次,关于整机成本,由于报销缘故,在设计之初从未考虑成本因素。但是现在来看很多选型和设计都是严重过剩的(预估本机成本在3k~2k,未包含探头),各位有意研究的朋友可以自行削减或修改电路。

也希望本次开源能为各位有这方面兴趣的朋友做一个研究的引导,为该方向的本科毕业生们提供一点毕设参考(也不用抄袭,因为这里已经上网了会查重到的哦)!

8.4 测试环境与图片展示

上图是主PCB实物图。

上图是最终成品实物图。换个角度看看探测器插头:

上图左侧的突出螺柱就是M12版前开孔的5针航空插头,淘宝能买。本文设计用来连接探测器,仪器向外提供+9V供电以及前放的输入。5根线可自己定义,空闲1根,直接焊板子上就行,预留了2.54mm排针焊接孔(对于AD_IN1和P1)

上图是测量用到的放射源Cs-137与Co-60源。

上图是自然本底能谱放大后的结果(只看黄色线),可以看到最高的峰是天然环境中K-40的贡献,他旁边是小峰是铀系计数,最右侧的小峰是钍系计数。

**云盘源文件***

由于vivado归档和vitis压缩后的源工程很大,故只能放云盘里上传了。文件中vivado和ip_core为FPGA项目及其打包的IP核,在vivado中可能需要重建文件路径及更新一下用户添加IP核的路径;vitis两压缩包为逻辑应用程序;qtdmca为上位机qt5项目源码;lvgl_dmca为LVGL图形界面设计工程,使用squareline 1.3.0 LVGLv8.2(vitis中移植好了LVGL v8.2)。/ 链接见文件docx,整个工程源码已完整开源!

文章中开发软件的版本告知:1. Vivado 2022.2;Vitis 2022.2; 2. Qt Creator 4.11.1 & Qt 5.14.2; 3. SquareLine Studio v1.3.0 & LVGL v8.2.0; 4. MATLAB R2021b

https://pan.baidu.com/s/19yhWbXKexZ7GzjkQz7AfXQ?pwd=sjv8

**其他告知**

首先关于装配,本文设计的3D外壳有些许尺寸误差。其一,4.8‘ LCD显示器螺丝孔位未对齐,文中使用热熔胶固定;其次,两PCB间使用5mm塑料螺柱连接(一定使用塑料),但是装配时发现接口比外壳高了约1mm,故需要切除螺柱1~2mm的高度再安装。见谅,暂未修改模型。

其次关于烧录,本文裸机程序有二,需要区分SPIFlash写入地址。amp为主程序,写入0x00地址中(默认不修改),开机默认启动;eth为网线连接的程序,写入0x7e0000。

关于焊接,PCB中较多电容特别在电源电路中,各位可酌情焊接。

作者能力有限,文中所言多有不妥,如有错误恳请各位指出修改!

开发周期:本文从立项到成品共耗时6个月,立项于2023年11月底,完整实现于2024年5月初,期间开发总花费4000元,完全个人研究成果。

由于本文工作量巨大,无法对每个细节面面俱到地讲解,本文和视频中只重点介绍了基础物理原理、硬件原理、FPGA算法部分,关于软件实在无法再细讲,但如果后续有空闲我还会继续补充。

**视频介绍**:

附件中视频1是使用操作说明、视频2是参数设置的讲解、视频3是测量及仪器原理的介绍、视频4作为放射源与测量测试环境的展示。

主要参考文献/书籍:

- 白彬. 2021. 基于Zynq的嵌入式双通道高速数字化谱仪的研制[D]. 成都:成都理工大学.

- 高乐. 2020. HPXe探测器数字多道系统研制及其基线漂移问题的算法修正[D]. 南京:南京航空航天大学.

- 葛青,葛良全,李晓丽. 2014. 基于冲激响应不变法的核信号数字滤波成形算法研究[J]. 核电子学与探测技术. 34(08):942-944+949.

- 洪旭,雷小兵,周建斌等. 2015. 新型极零相消电路数学模型的建立与实现[J]. 中国测试. 41(10):94-97.

- 洪旭,倪师军,周建斌等. 2016. 梯形成形算法中成形参数与成形脉冲波形关系研究[J]. 核电子学与探测技术. 36(02):150-153+158.

- 李传江. 2016. 低功耗便携式γ能谱仪的设计与实现[D]. 北京:中国科学院大学(工程管理与信息技术学院).

- 李逢伟. 2014. 基于FPGA和USB的数字化多道脉冲幅度分析系统[D]. 兰州:兰州大学.

- 卢希庭. 2010. 原子核物理. 第二版. 北京:原子能出版社. ISBN:9787502221881.

- 史宏涛. 2022. 通用型数字化多道脉冲幅度分析器的设计[D]. 南昌:东华理工大学.

- 王剑宇. 2010. 高速电路设计实践. 北京:电子工业出版社. ISBN:9787121101311.

- 杨剑. 2018. 高纯锗数字多道脉冲幅度分析系统的研制[D]. 成都:成都理工大学.

- 周建斌,周伟,王敏. 2017. 核信号数字分析与处理. 北京: 中国原子能出版社. ISBN: 9787502278038.

- 张羽中,肖无云,李京伦等. 2018. 精密多道脉冲幅度分析器设计[J]. 核电子学与探测技术. 38(06):847-851.

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程

评论