杰理音频发生器

简介

用杰理的蓝牙音箱芯片制作一个手持的音频(波形)发生器,用于调试音频放大电路和维修。

简介:用杰理的蓝牙音箱芯片制作一个手持的音频(波形)发生器,用于调试音频放大电路和维修。开源协议

:MIT License

描述

一、团队介绍

一个人的团队,骨灰级DIY爱好者。

没有参赛经验,但有设计的欲望和热情;

退休啦,不愿意用广场舞打发时间,喜欢和朝气蓬勃的年轻人一块儿学习进步。

二、题目要求

本次比赛旨在创作者设计出具有创新性和实用性的音频类电子产品。

知识老化严重,创新性还需要向年轻人学习,这次就把重点放在实用性吧。做一个手持的音频信号发生器。

三、设计摘要

玩电子经常会接触到模拟信号;一个输出可调的音频波形发生器就很有必要。不但可以方便调试模拟放大电路,也可以为数字采样电路测试提供稳定且可重复的信号源;甚至可以为DCDC变换器提供临时的PWM波形。

四、题目分析

制作一个手持的音频(波形)发生器,用于调试音频放大电路和维修。

具有以下功能:

1、1Hz-3kHz音频范围内的正弦波(耳放)输出;

2、1Hz-3kHz三角波可调频率输出;

3,、彩色液晶用户界面,按键操作;

4、小型化手持设备,锂电池长时间待机模式;

杰理的蓝牙音箱芯片功能强大,很适合手持类、低功耗、长待机的应用。杰理AC6904可以满足手持音频波形发生器的所有功能要求。

五、总体设计框图

作为工具使用,可靠和稳定十分必要;功能过多会增加操作复杂性。本着极简的原则,仅使用2个按键作为输入,输出使用缝衣针作为端子,方便微小电路板的调试。为了用户界面更直观,使用了一片彩色液晶屏作为用户界面。

1:输入部分,两个独立按键,实现开关机和菜单选择

2:输出部分,芯片耳放直接探针输出

3:电源管理,完全由芯片内部模块实现,外接元件仅为电容

4:人机界面,160*80字符+图形显示菜单

5:一个板载喇叭可选择打开,监听输出内容

六、硬件电路组成

如无必要勿增实体,基本就是标准的音箱电路,并删除了蓝牙和收音机外围阻容和天线。

电路很简单,直接看原理图吧。

因为是一个辅助信号源,把右手留给更重要的事情,所以设计适合左手持握。

频率发生器的核心代码都已经测试无误;目前尚未完成人机交互的界面设计;

主要是两个按键和一片TFT显示屏,用来选择需要输出的频率和幅度;以及是否需要辅助音频输出。

七、程序流程图

程序和数据是本设计的重点,需要较长的篇幅说明。

遵循以下设计原则:

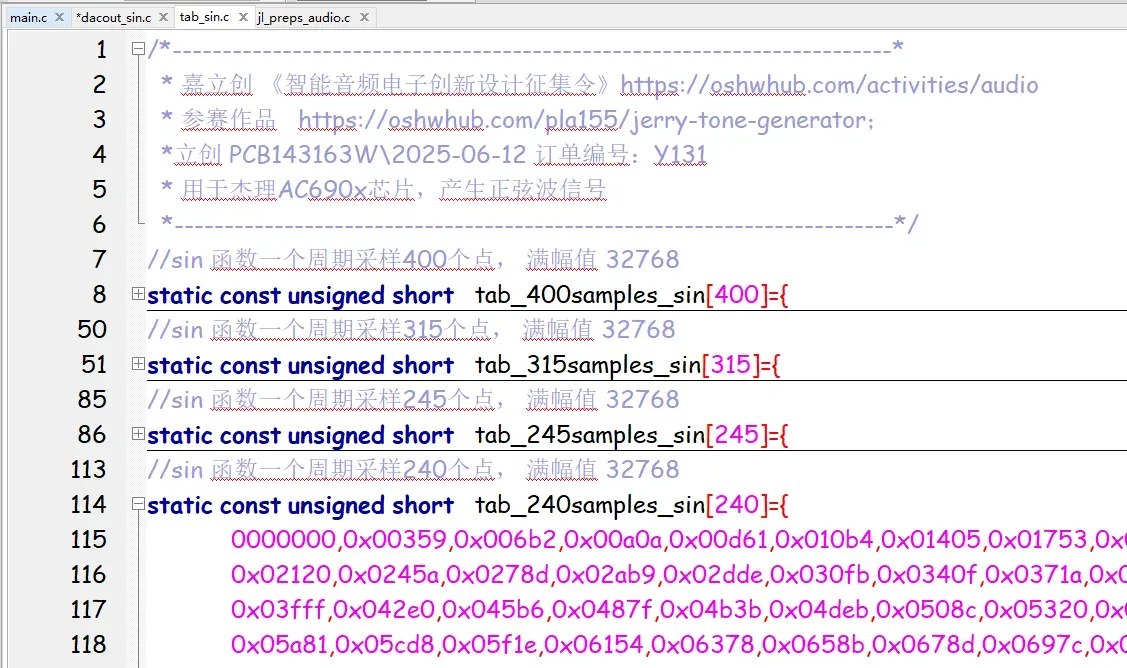

1,为精简空间存放更多波形数据,不使用官方SDK库函数

2,程序功能块设计,方便今后升级

3,保留串口测试功能,方便使用者可能的自定义任意波形

先来了解一下杰理的audio模块功能:

杰理的audio模块分为两个子模块:DAC和ADC;DAC模块包含左右两个立体声通道,独立工作但同时使能。DAC的数据深度为16位,频率范围可以10档: 44100;48000;32000;22050;24000;16000;11025;12000;8000。DAC使用主频异步的时钟源,默认是PLL的24M分频,也可以是LSB时钟。LSB时钟源或许可以为我们提供高于48K的时间精度。

DAC使用兵乓结构的双缓冲数组,左右声道数据是交叉排列在缓冲区的,地址要求4字节对齐。

音频发生器比声音数据的处理简单,不需要兵乓结构,也不需要在中断里处理数据缓冲和指针的更新。只需要把数据放入缓冲区就可以反复使用同一数组内容。

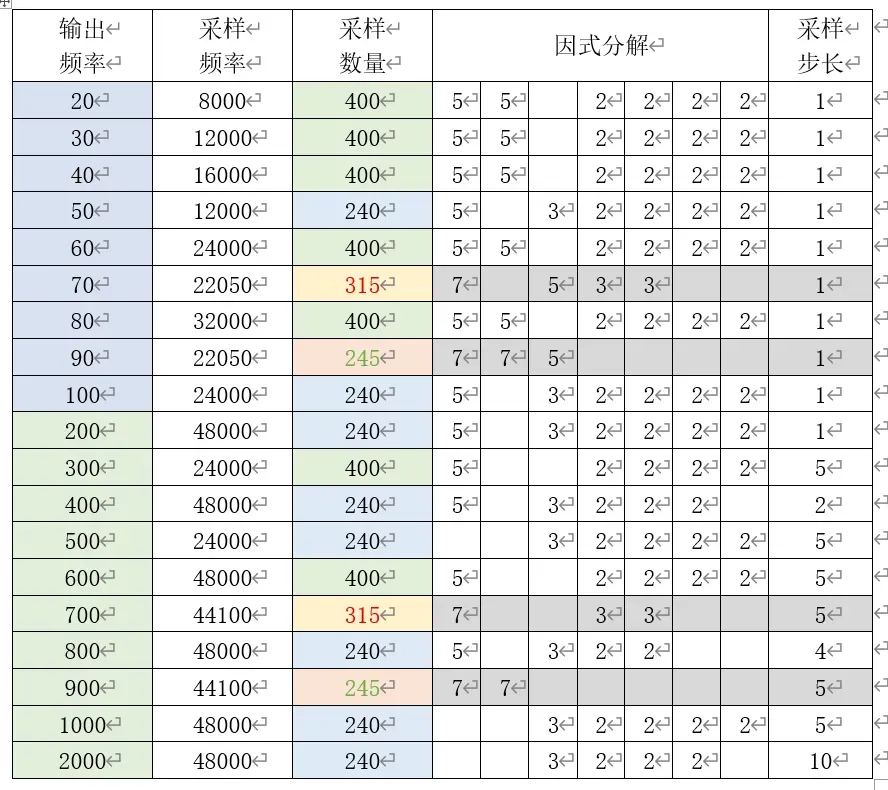

DAC最高频48K ;为保证1/4周期数据点位不少于5个,上限频率只做到2KH;低频部分,简化代码设计,从20Hz开始。

使用两组基准正弦波数据包,一组1200(= 5532222)个采样点,另一组2205(= 77533)个采样点,方便各频率抽组数据。

为了编程简单,生成了4个数据采样矩阵,矩阵采样点数为个目标频率的最小公倍数。

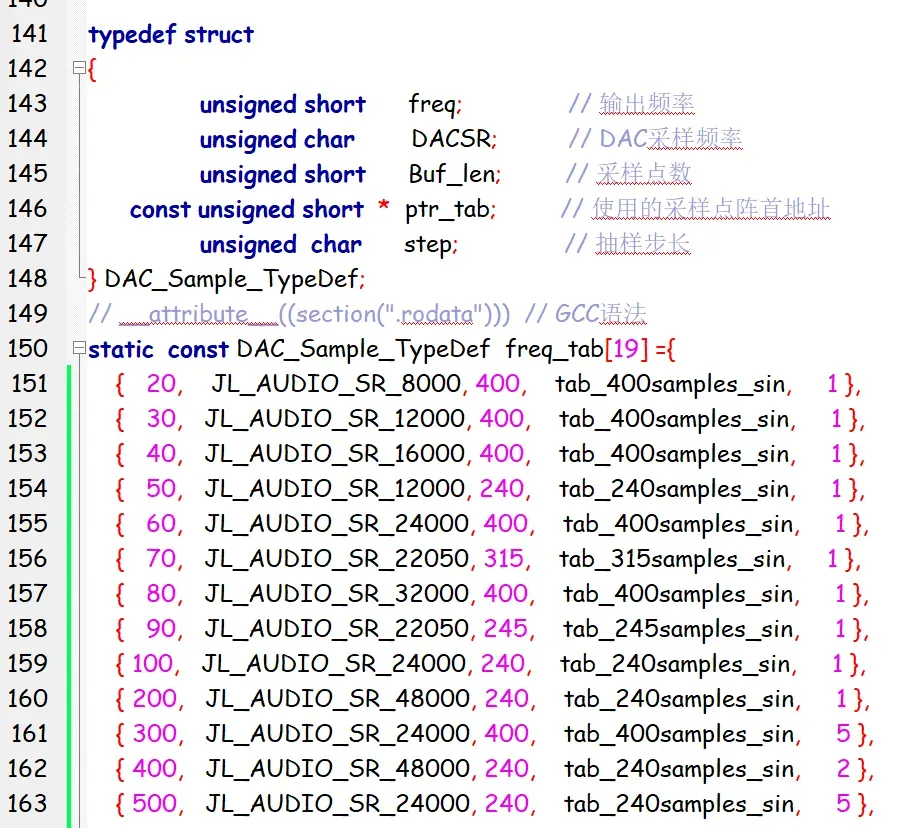

定义了一个结构体数组,来存放上图所需的关键数据

核心代码就是一个按采样频率进行原始数据抽样的过程

#include

/------------------------------------------------------------------------/

void Dac_Out_freq(unsigned char n)

{ unsigned short i , j ;

const unsigned short * ptr = freq_tab[n].ptr_tab;

//---------------------------------

j = 0;

for( i= 0 ; freq_tab[n].Buf_len>i ; i+=freq_tab[n].step)

{ Audio_Dac_Buf[j++] = ptr[i];

Audio_Dac_Buf[j++] = ptr[i];

}

for( i= 0 ; freq_tab[n].Buf_len>i ; i+=freq_tab[n].step)

{ Audio_Dac_Buf[j++] = ptr[i];

Audio_Dac_Buf[j++] = ptr[i];

}

//---------------------------------

JL_AUDIO->DAC_ADR = (uint32_t) Audio_Dac_Buf;

JL_AUDIO->DAC_LEN = freq_tab[n].Buf_len/freq_tab[n].step;

JL_AUDIO->DAC_CON_bit.DACSR = freq_tab[n].DACSR ; // DAC sampling rat

JL_AUDIO->DAC_CON_bit.DACEN = 1; // DAC 数字模块打开

// --------------------------------

return ;

}

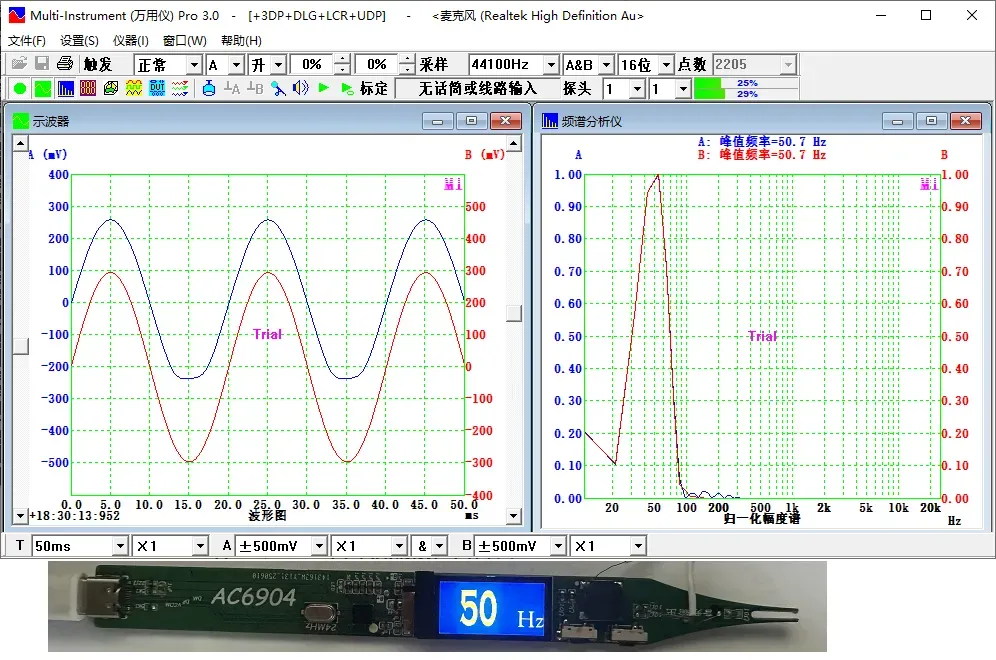

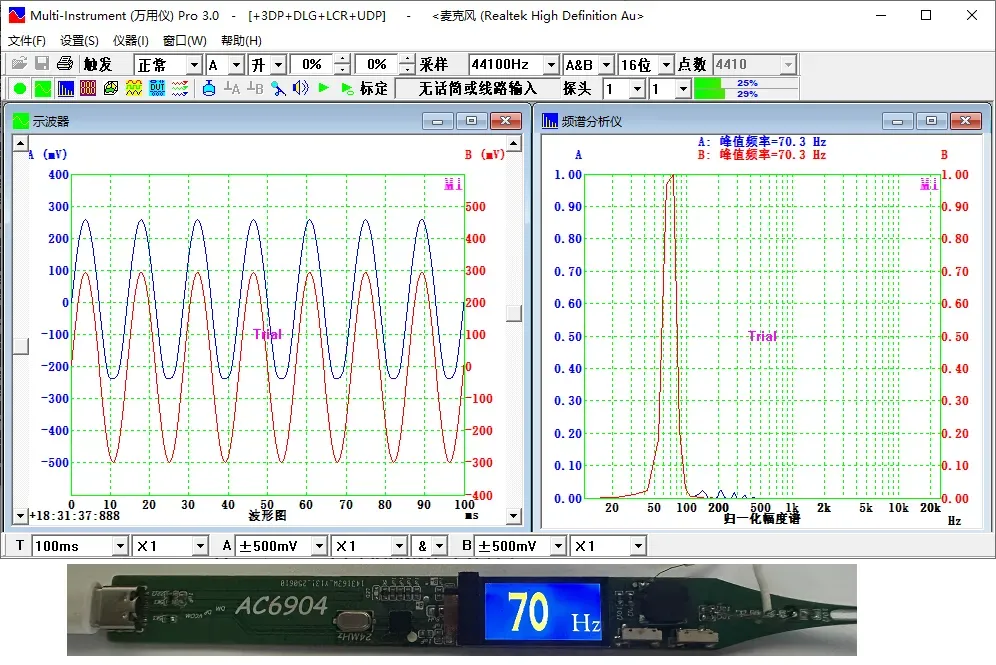

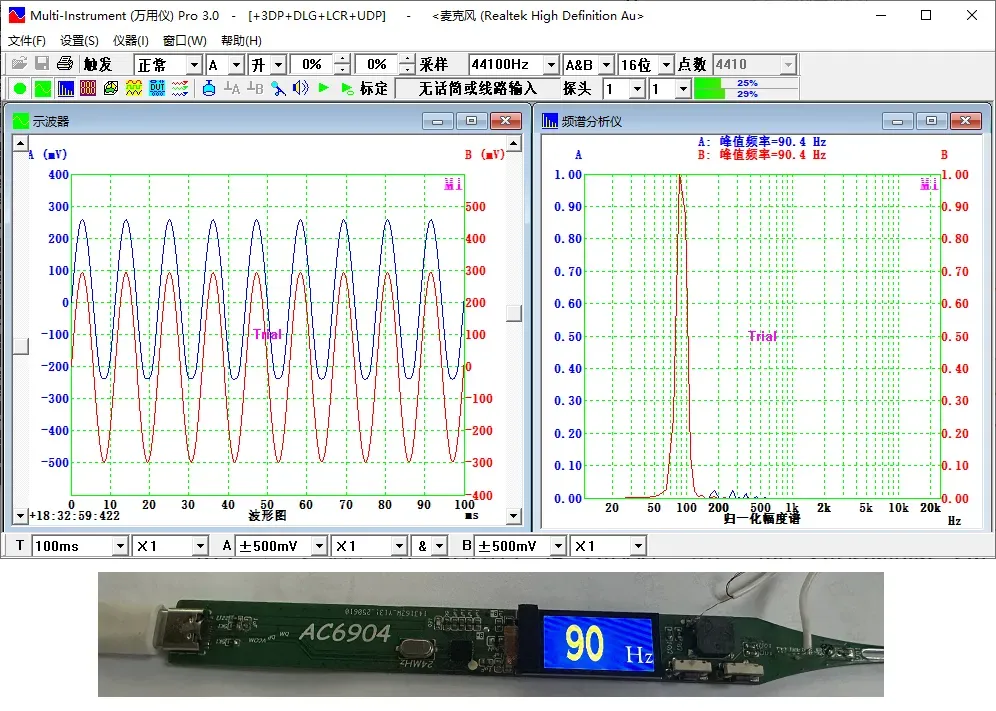

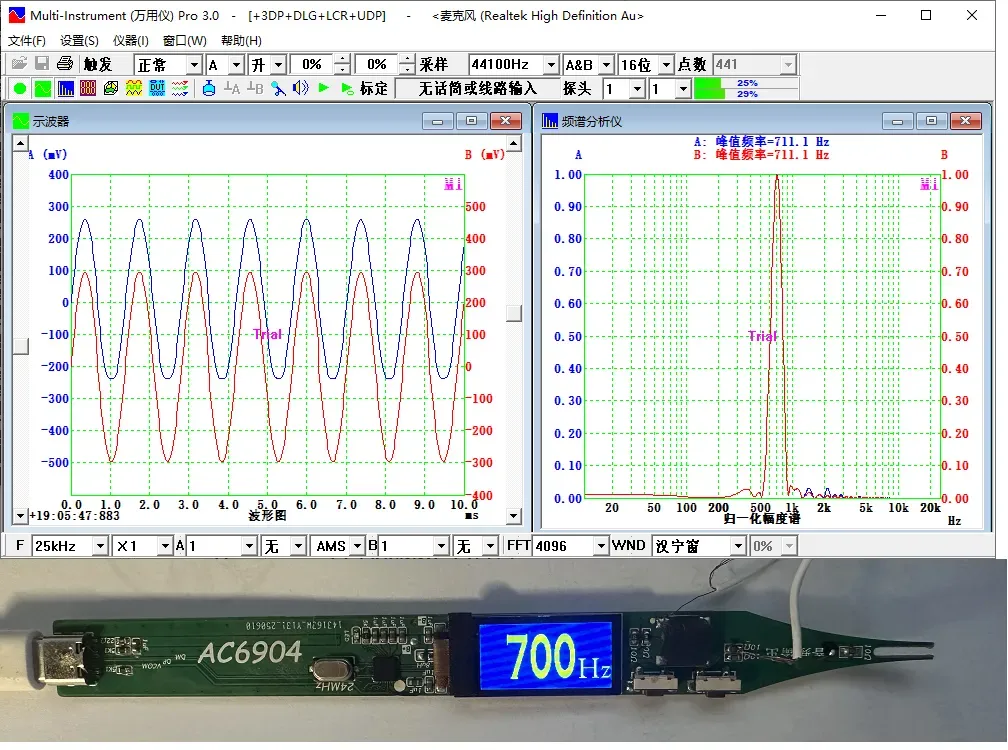

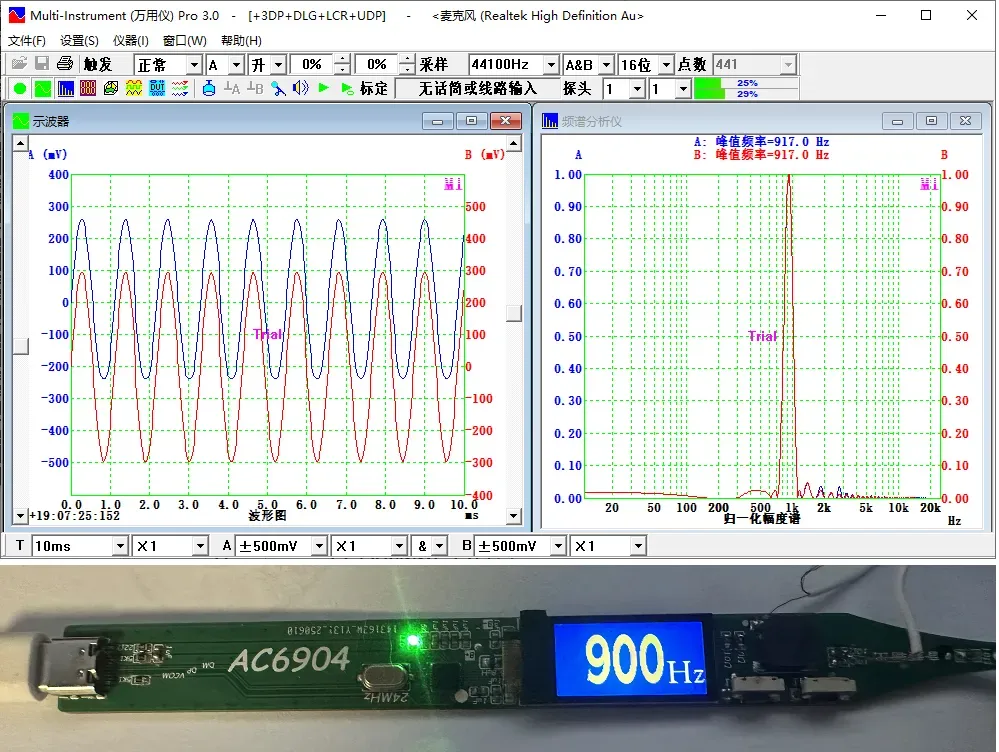

八、实物展示

实物测试图,使用声卡示波器测试,并附有频谱分析结果

九、注意事项

设计注意事项:

1、 DCDC电源电路,布局时尽量靠近 SW引脚,走线尽量短和宽 ,不要有过孔。

使用绕线电感或功率叠层电感,阻抗尽量小一些 ,额定电流大于120mA,内阻小于0.5R。

2、 PGND不分地,就近接数字GND。

3、 DAC模拟部分走线应尽量远离开关电源部分,远离GND走线。

4、 PR1, PR2, PR3为唤醒IO,高低电平都可以唤醒。按键开关机唤醒请使用PR2口低电平

唤醒,因PR2长按有复位功能 (低电平复位有效 ),可解决特殊情况死机不开机问题。

5、主控所有电源的退耦电容必须靠近芯片放置 ,退耦电容的回路地必须最短回到该电源地

6、主控不断电,最低待机功耗大概4uA以下。

7、为保证安全可靠性,电池必须使用带保护板的电池。

8、USBDP、 USBDM预留测试口,以备开发升级程序用。

9、充电输入端串限流电阻,以满足充电电流大小的需求。

十、演示视频

提示:演示视频上传附件即可,附件最大只能长传50M的文件,大于50M的文件可放置在其他网盘或视频网站上,只需把地址链接放入这里即可

十一、附件内容

提示:参加活动的作品必须把工程相关的程序附件上传至开源平台或个人的代码存储云端,附件最大支持50M上传(请勿在立创工作区上传,有限制)附件按以下要求进行命名:

附件一:主函数

附件二:DAC输出函数

附件三:数具表

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程

评论