开源高速ADC_LTC2208

简介

基于16位135Msps LTC2208的高速ADC设计,参考B站up主TerayTech同款芯片开源,电源重新设计,可供对电源精度与效率要求高的应用提供参考,已迭两代,建议参考新版V1.1,6层板

简介:基于16位135Msps LTC2208的高速ADC设计,参考B站up主TerayTech同款芯片开源,电源重新设计,可供对电源精度与效率要求高的应用提供参考,已迭两代,建议参考新版V1.1,6层板开源协议

:GPL 3.0

描述

LTC2208与其周边电路

综述:LTC2208:流水线分级式ADC130Msps 16bits

差分模拟量输入,differental范围:可选1.5Vpp或2.25Vpp

CMOS或 LVDS数字输出

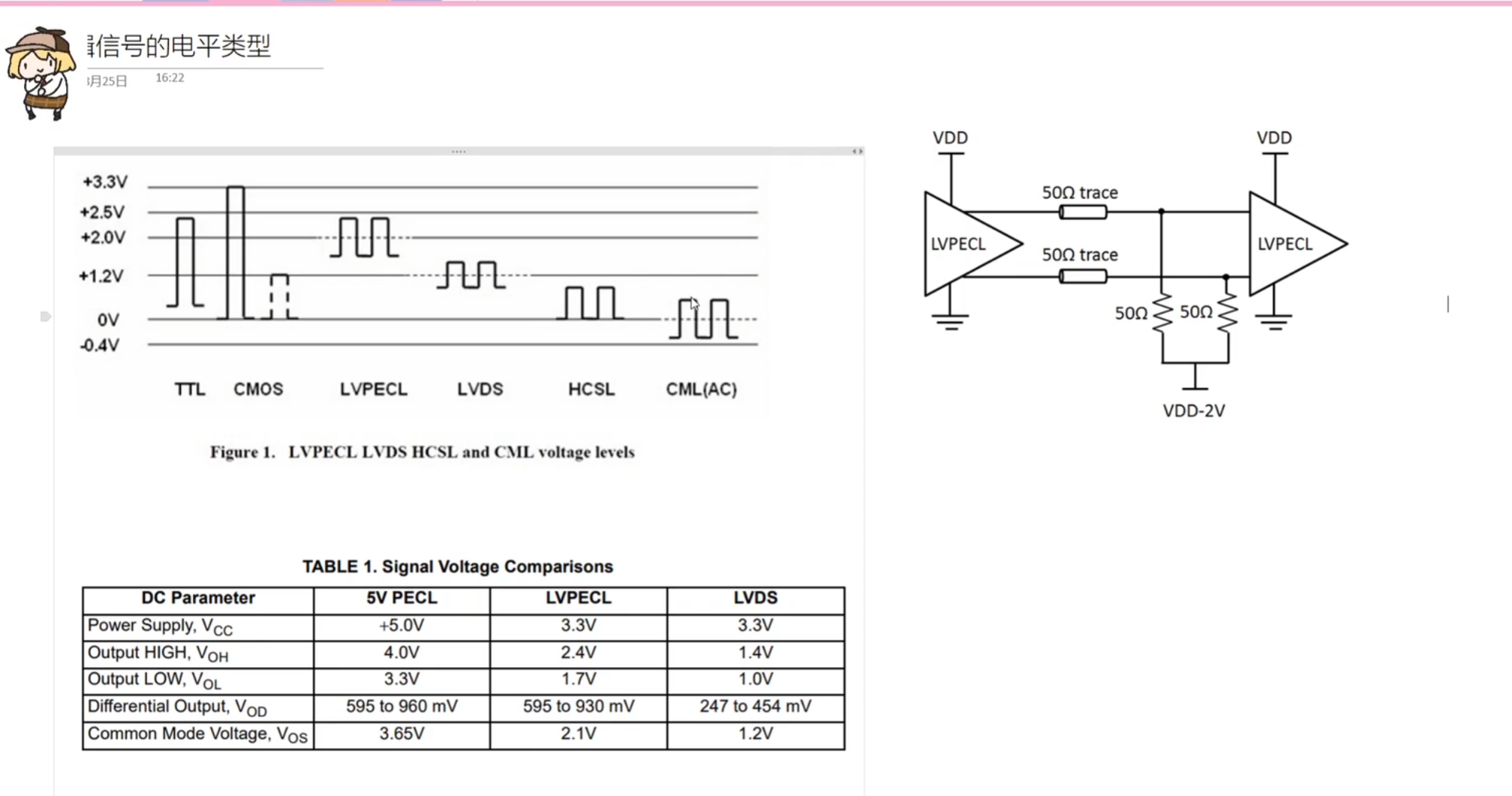

差分时钟输入,较灵活,可以LVPECL,LVCMOS和别的(满足手册范围即可)

参考灵活,可使用内部或外部参考源

配置简单,使用外部电阻而非SPI

注意:建议将手册完完整整认真读一遍,并结合本篇参考,一切以手册为准

这芯片的手册写的特别好,可以学到很多东西

配置引脚定义

接上拉0电阻:默认高电平

接下拉0电阻:默认低电平

未定的标黄,红色为我的参考配置

配置(CMOS)

1.SENSE(Pin 1): VDD:内部参考(V1.0)

2.5/1.25:外部参考2.5/1.25源(V1.1)

2.SHDN(Pin 19): 拉高:关闭 数字输出为高阻态(用下拉电阻)

3.DITH(Pin 20):高电平使能内部dither,难决定,先接地失能

4. LVDS pin(Pin 61): 接地

5. MODE (Pin 62):见手册p15(排列组合)(数据输出格式与时钟输入占空比)

2/3Vdd使用内部PLL,与补码数据格式

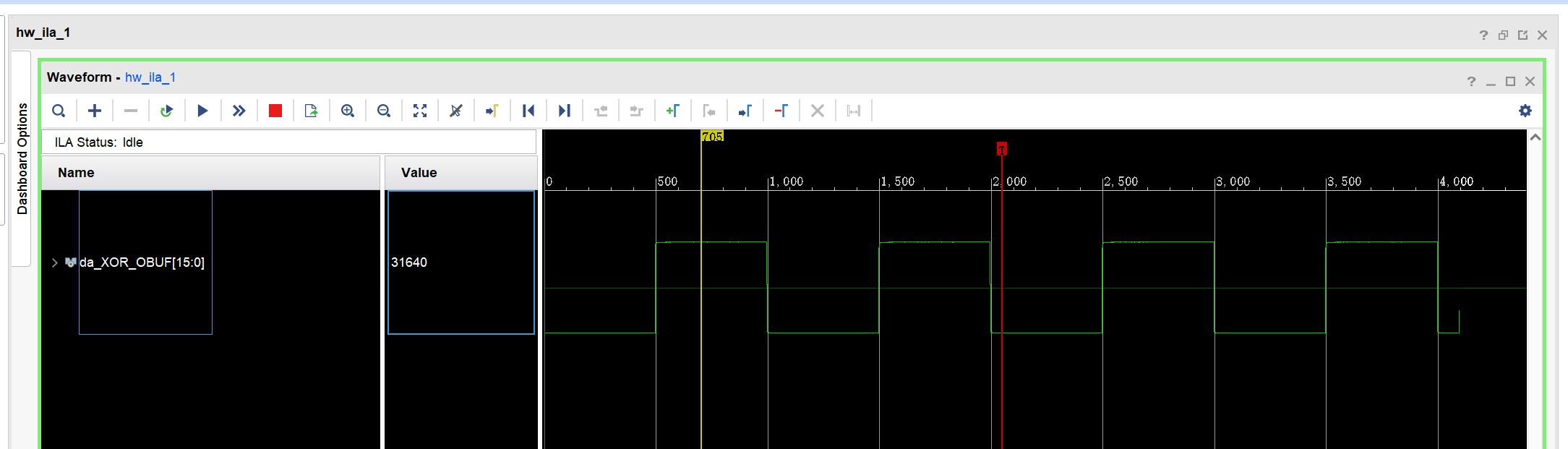

6. RAND (Pin 63):低电平正常输出,高电平D1-D15均与D0(LSB)异或(减小数字信号耦合影响)高电平

7. PGA (Pin 64):低电平2.25Vpp输入,高电平1.5Vpp输入.

手册P17:术语定义

手册P25:低电平输入时抖动(dither)

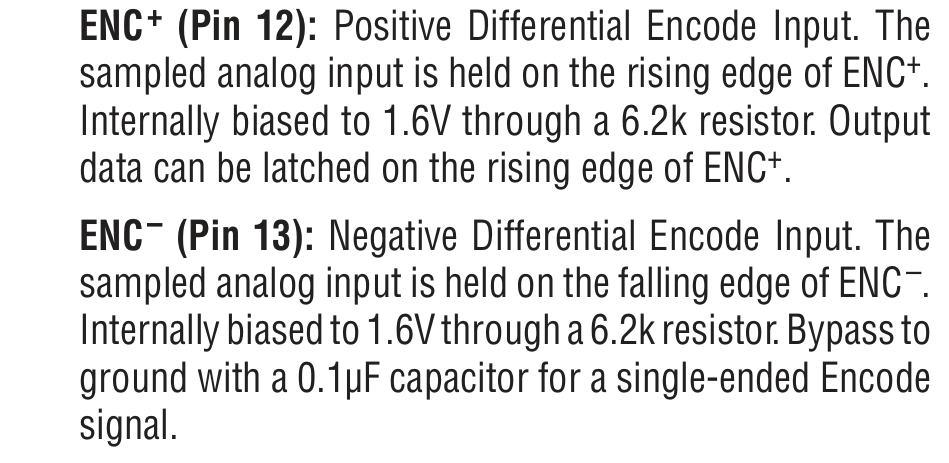

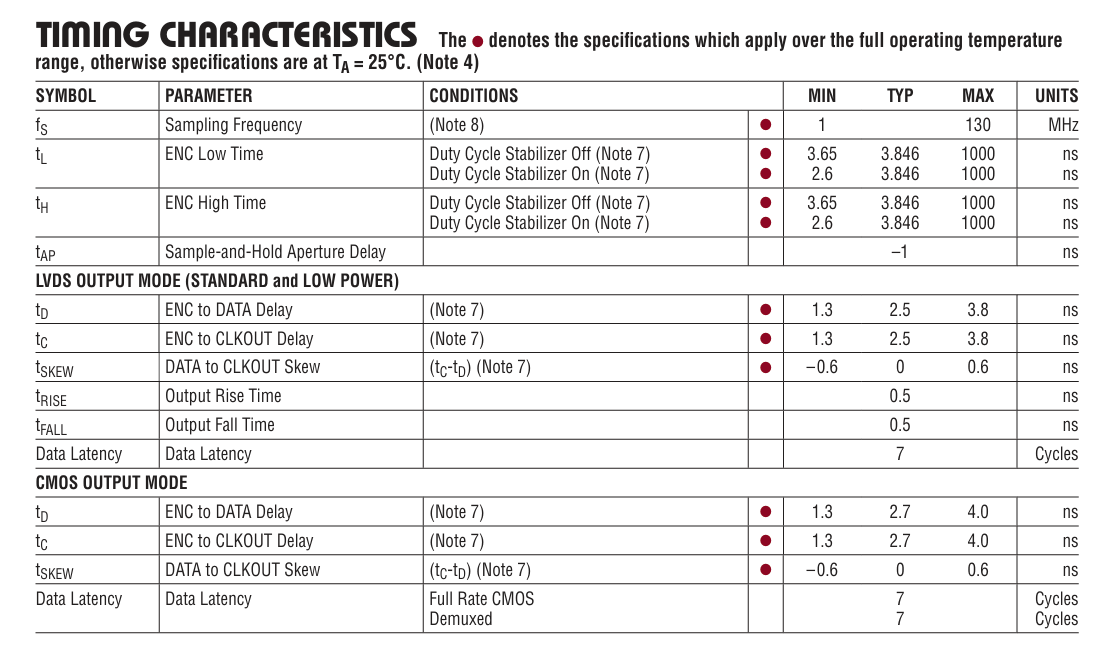

时钟(ENC+/ENC-)输入

ENC+ (Pin 12): Positive Differential Encode Input. The sampled analog input is held on the rising edge of ENC+. Internally biased to 1.6V through a 6.2k resistor. Output data can be latched on the rising edge of ENC+.

ENC– (Pin 13): Negative Differential Encode Input. The sampled analog input is held on the falling edge of ENC–. Internally biased to 1.6V through a 6.2k resistor. Bypass to ground with a 0.1μF capacitor for a single-ended Encode signal.

The encode inputs have a common mode range of 1.2V to VDD.

若输入的占空比不是50,则mode必须为1/3或2/3VDD

最慢1Msps

V1.0/V1.1:均采用外部CMOS输入经SN65LVELT22DR转LVPECL

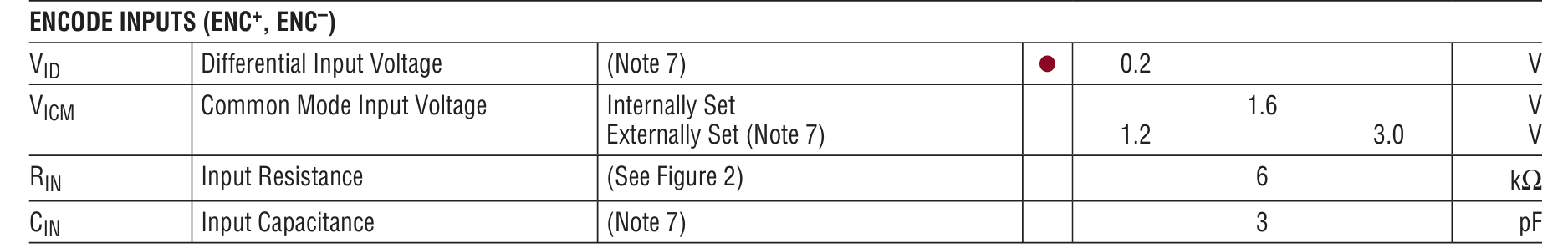

时间特性

手册还有经典时序图

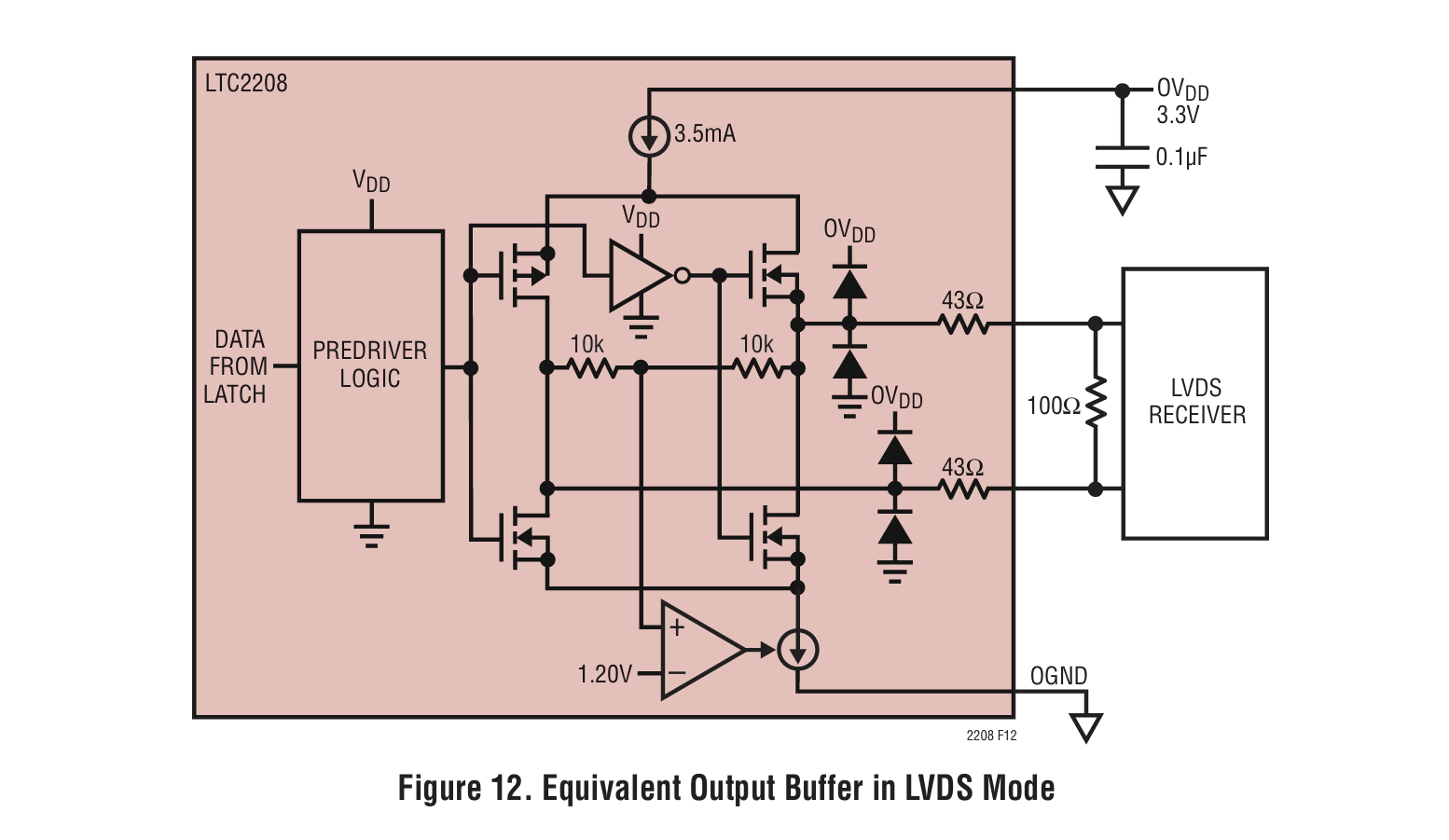

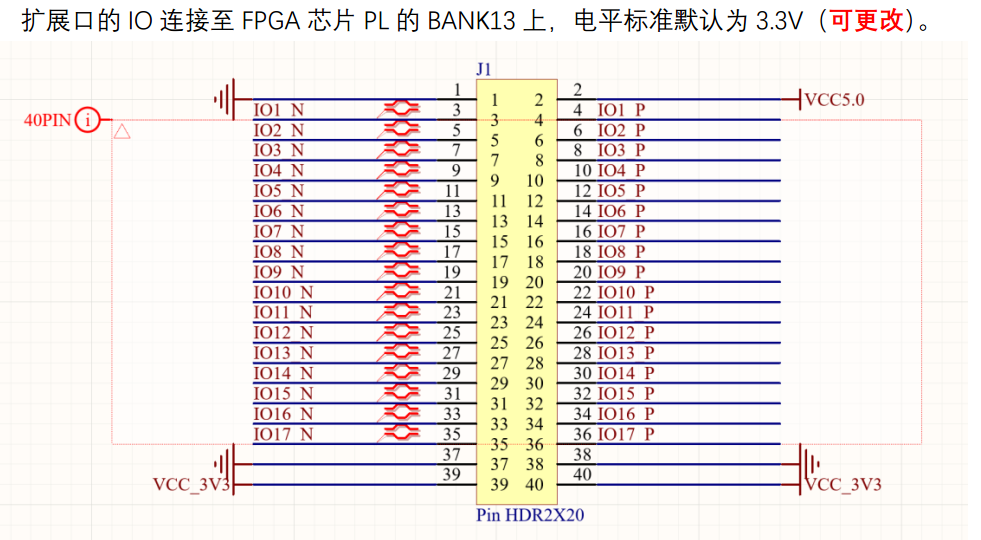

LVDS数字输出

D0-/D0+: LSB

D0–/D0+ to D15–/D15+:要求差分100欧终端电阻

D15+/D15– is the MSB

CLKOUT–/CLKOUT+ (Pins 39 and 40): LVDS Data Valid 0utput. Latch data on the rising edge of CLKOUT+, falling edge of CLKOUT–.

见 手册p23

CMOS数字输出

引脚定义与LVDS不同,注意

DA0-DA15

内部有源端50欧电阻,外部可不加

需挂载 < 10pF容性负载(ALVCH16373)(应该可不管它)

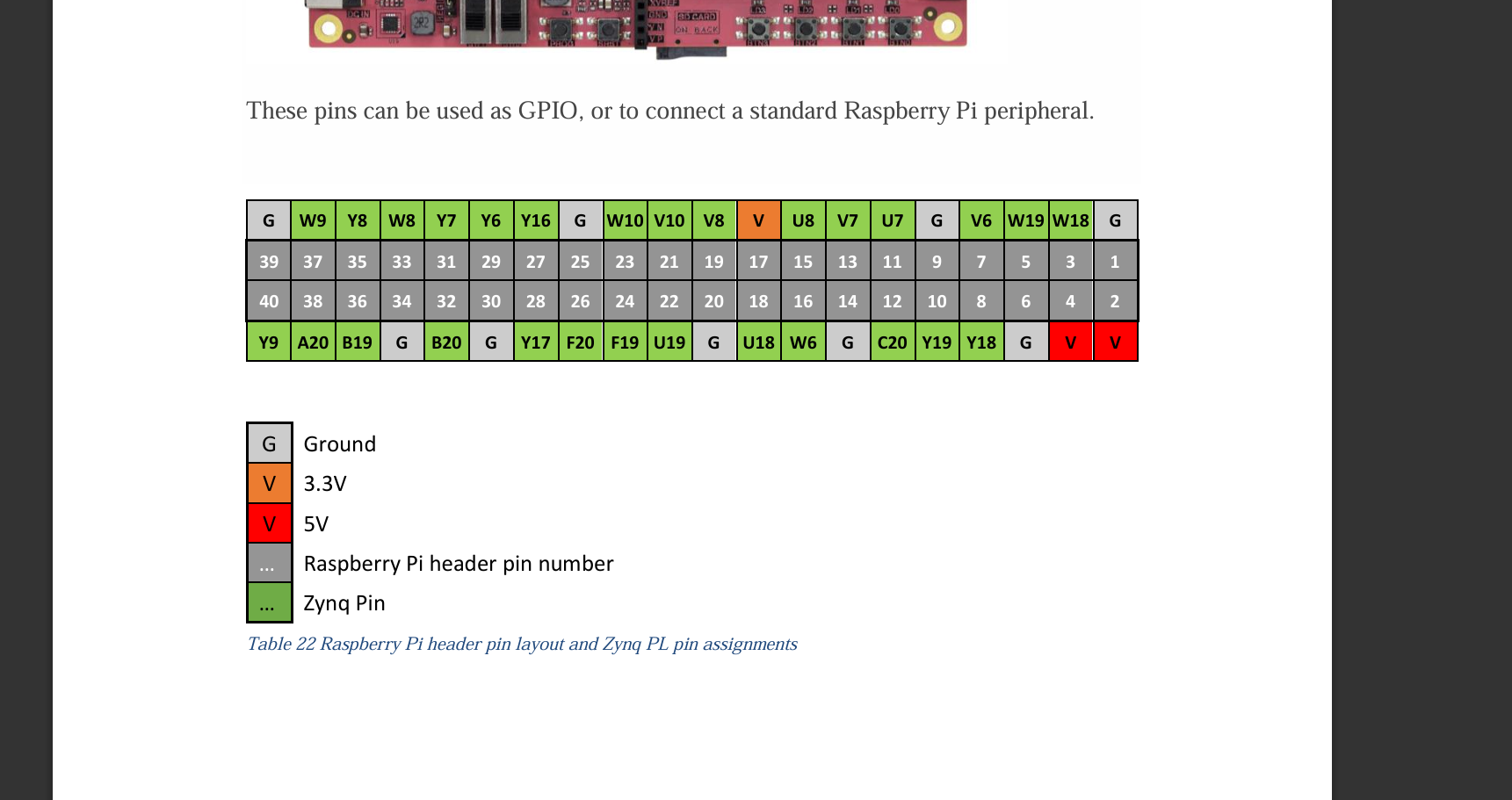

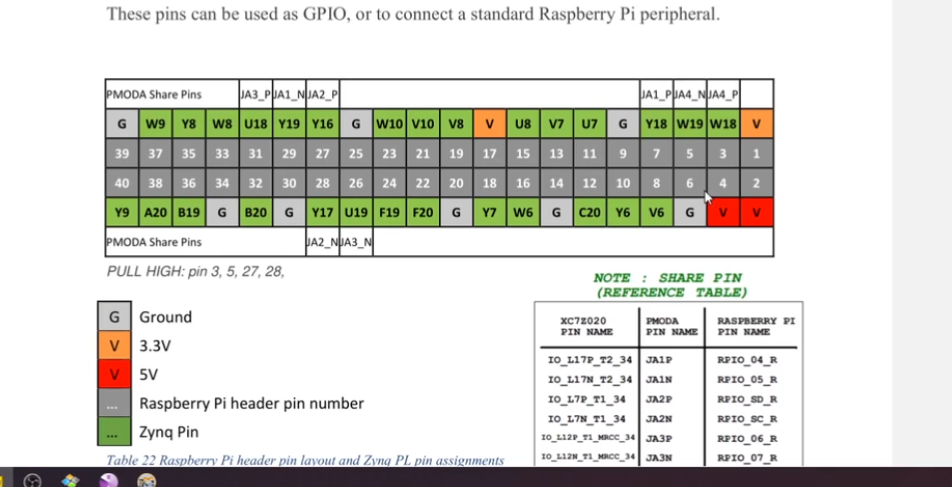

V1.0 :40pin 2.54mm排针兼容PYNQ2

V1.1: 40pin 2.54mm排针兼容黑金与淘宝RIGUKE的zynq 7020板子

模拟输入级

两版均采用直流耦合

V1.0采用一级全差分运放,输入阻抗50欧,电阻需使用精密电阻(电阻计算参考ADI的全差分运放工具)

V1.1采用两级,先经过跟随器(或同相比例放大器)后接全差分运放,不需使用精密电阻且可选输入高阻或任意阻抗

参考源

V1.0是用的内部

V1.1使用外部高精度ADR4525B

建议最好使用外部,因为该ADC功率较大(1.5W),温升很严重(最坏情况下达到90度,建议使用温升小的外部参考源)

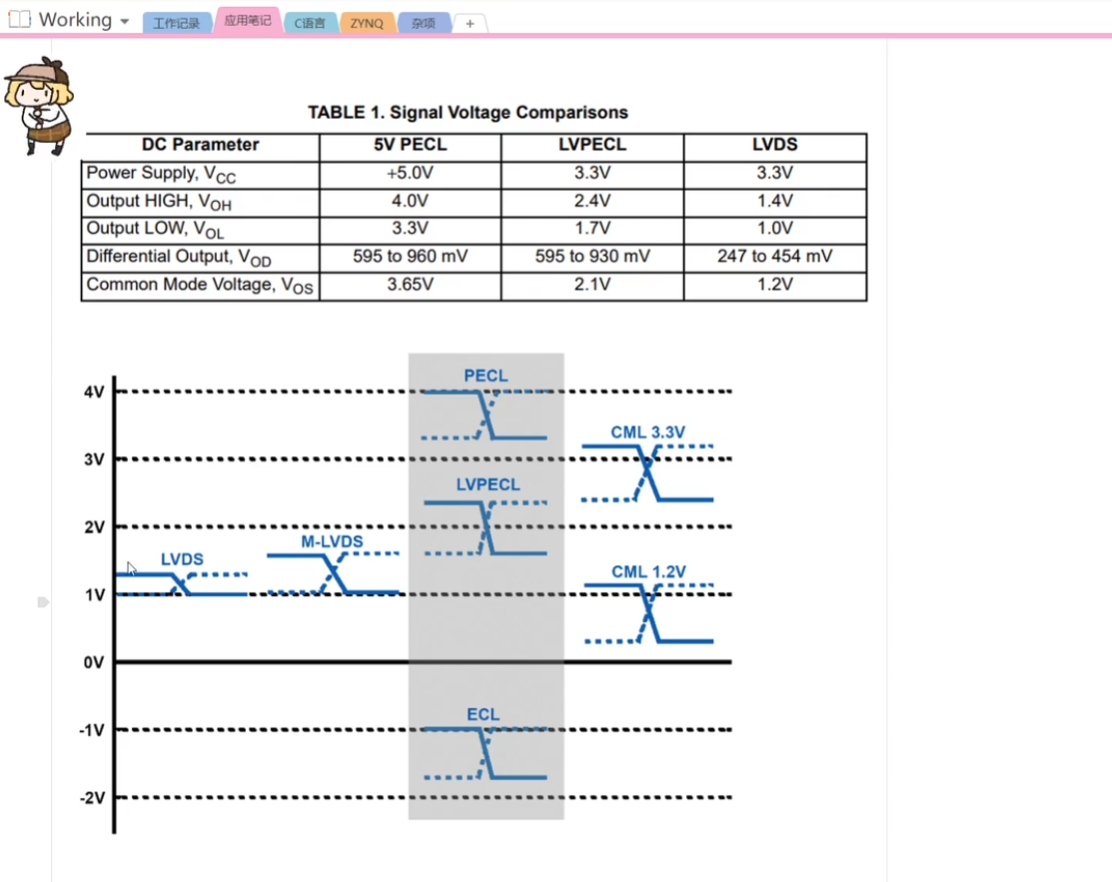

补充:各种逻辑电平

参考b站up主TerayTech 《终端电阻》的视频

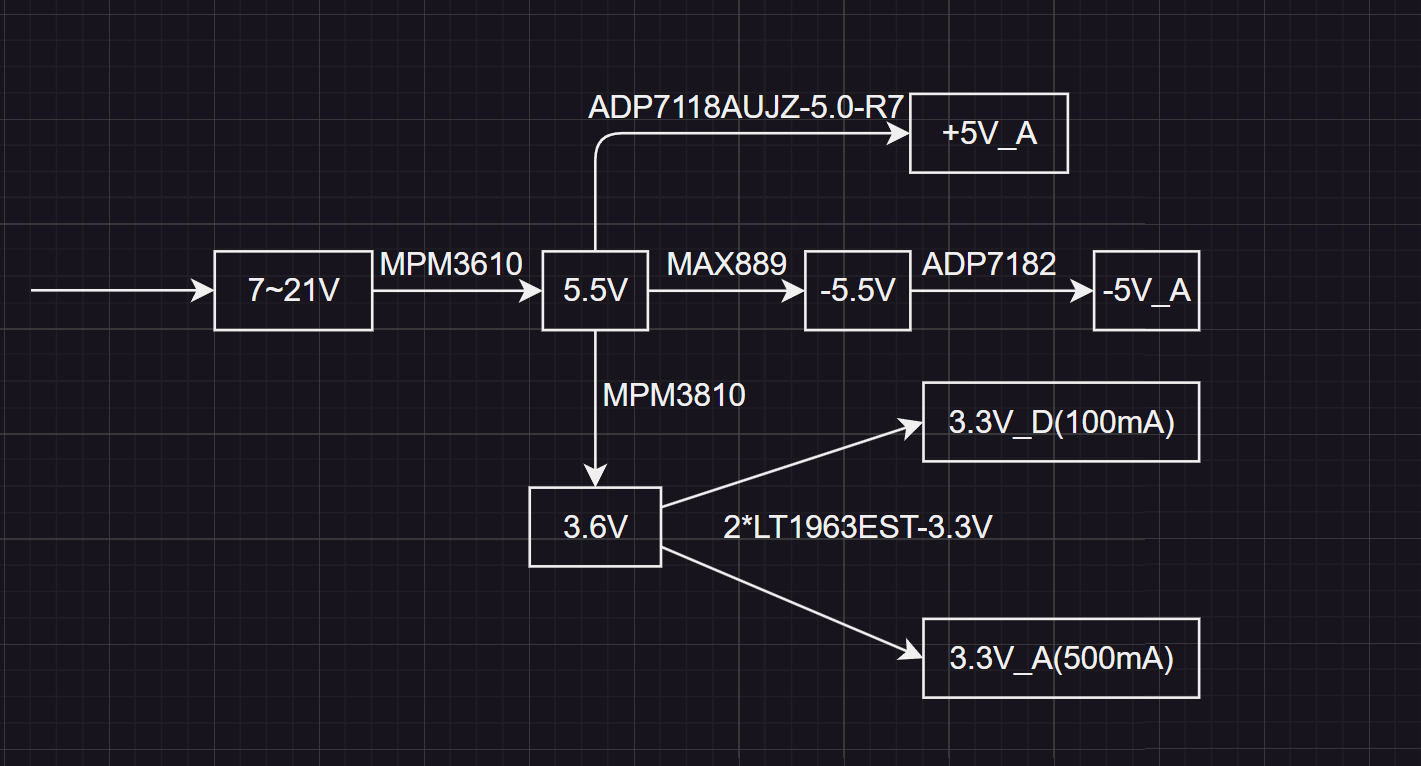

板级电源方案

该方案适配各种对于电源纹波精度要求高的场合,同时做到了高效率。

(注:请看V1.1的,V1.0设计存在非常大问题)

(注:不可实际用于产品,有很多是用的拆机片)

选型方案

LDO

正转正LDO:

TPS74401:低成本高性能

LT1963(小封装固定3.3/2.5/1.8,大封装可调):1.5A若要5V则仅可用大封装(ES:SOIC-8)

ADP7118(小封装5/3.3/2.5/1.8):200mA精密 (ADP151也行,便宜,但没有5V的)

负转负LDO :

ADP7182/ADP7183(小封装): 精密场合(7183有大电流500mA但是待找)

LT3015(大封装): 大电流1.5A

LT1964(小封装):200mA

DCDC

在板级上使用MPS集成内部电感的MPM模块是首选(外部电路简单)

高压输入:用MPM36xx(4.5~21V) MPM35xx(36V)

<6V输入:用MPM38xx

若需更高功率建议使用常规的内部开关管buck芯片,如TPS54360(可至3A)

负电源

用反相电荷泵是最简单的 MAX889(200mA)

若要大功率:用buck-boost拓扑的开关电源(常规buck芯片一般支持,如TPS54360)

具体方案(V1.1)

依据:1.数字芯片可直接用开关电源供电,而模拟芯片建议最好用LDO供电

2.5V转3.3V 直接使用LDO在高功率需求时效率过低且发热严重,所以建议经过DCDC5V转3.6V左右后经过低压降LDO再转3.3V

由于功率冗余还外接提供5.5V输出口

具体请见原理图

V1.1已验证,基本功能正常,噪声,失真等参数待测

复刻注意:

1.使用了X2Y电容,若不使用,请为全差分运放添加滤波电容

2.有些芯片不常见,但基本能在淘宝买到

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程

评论